US010269874B2

(12) **United States Patent**

**Madigan**

(10) **Patent No.:** **US 10,269,874 B2**

(45) **Date of Patent:** **\*Apr. 23, 2019**

(54) **HIGH RESOLUTION ORGANIC

LIGHT-EMITTING DIODE DEVICES,

DISPLAYS, AND RELATED METHODS**

(71) Applicant: **Kateeva, Inc.**, Newark, CA (US)

(72) Inventor: **Conor F. Madigan**, San Francisco, CA (US)

(73) Assignee: **Kateeva, Inc.**, Newark, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: **15/406,455**

(22) Filed: **Jan. 13, 2017**

(65) **Prior Publication Data**

US 2017/0236883 A1 Aug. 17, 2017

**Related U.S. Application Data**

(63) Continuation of application No. 14/030,776, filed on Sep. 18, 2013, now Pat. No. 9,614,191.

(Continued)

(51) **Int. Cl.**

**H01L 27/32** (2006.01)

**H01L 51/00** (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC ..... **H01L 27/3218** (2013.01); **H01L 27/3246** (2013.01); **H01L 51/0005** (2013.01);

(Continued)

(58) **Field of Classification Search**

CPC ..... H01L 27/3218; H01L 27/3246; H01L 51/0005; H01L 51/5012; H01L 51/5056;

(Continued)

(56) **References Cited**

**U.S. PATENT DOCUMENTS**

5,541,479 A 7/1996 Nagakubo

6,294,398 B1 9/2001 Kim et al.

(Continued)

**FOREIGN PATENT DOCUMENTS**

CN 1770938 A 5/2006

CN 1841763 A 10/2006

(Continued)

**OTHER PUBLICATIONS**

Applicant Initiated Interview Summary dated Apr. 29, 2016, to U.S. Appl. No. 14/156,188.

(Continued)

*Primary Examiner* — Didarul A Mazumder

(74) *Attorney, Agent, or Firm* — Paula J. Tostado

(57) **ABSTRACT**

A method of manufacturing an organic-light emitting diode (OLED) display can include providing on a substrate a first electrode associated with a first sub-pixel and a second electrode associated with a second sub-pixel, wherein a gap is formed between the first electrode and the second electrode and wherein the first electrode and the second electrode are positioned in a well having boundaries defined by a confinement structure on the substrate. The method can also include depositing in the well with the electrodes positioned therein, active OLED material to form a substantially continuous layer of active OLED material that spans the boundaries of the well such that a surface of the layer of active OLED material that faces away from the substrate has a non-planar topography. The depositing can be via inkjet printing.

**27 Claims, 17 Drawing Sheets**

## Related U.S. Application Data

(60) Provisional application No. 61/753,692, filed on Jan. 17, 2013.

2014/0078126 A1 3/2014 Hack et al.

2017/0062536 A1 3/2017 Madigan

2017/0309691 A1 10/2017 Madigan

2018/0294324 A1 10/2018 Madigan

2018/0315963 A1 11/2018 Madigan

## (51) Int. Cl.

*H01L 51/50* (2006.01)

*H01L 51/52* (2006.01)

*H01L 51/56* (2006.01)

## (52) U.S. Cl.

CPC ..... *H01L 51/5012* (2013.01); *H01L 51/5056* (2013.01); *H01L 51/5088* (2013.01); *H01L 51/5206* (2013.01); *H01L 51/5221* (2013.01); *H01L 51/56* (2013.01); *H01L 2251/301* (2013.01); *H01L 2251/308* (2013.01); *H01L 2251/558* (2013.01)

## (58) Field of Classification Search

CPC ..... H01L 51/5088; H01L 51/5206; H01L 51/5221; H01L 51/56; H01L 2251/301; H01L 2251/308; H01L 2251/558

USPC ..... 257/40; 438/82, 99

See application file for complete search history.

## FOREIGN PATENT DOCUMENTS

EP 1708294 A2 10/2006

EP 1601032 B1 6/2012

GB 2437110 A 10/2007

JP 2001143868 A 5/2001

JP 2005203351 7/2005

JP 2006127783 A 5/2006

JP 2006310257 A 11/2006

JP 2007018775 A 1/2007

JP 2009187730 A 8/2009

JP 2010021138 A 1/2010

JP 201034143 A 2/2010

JP 2010141059 6/2010

JP 2010186582 8/2010

JP 2011113982 6/2011

JP 2012028180 2/2012

JP 2013004517 A 1/2013

TW 201244222 A 11/2012

WO 2009097377 A1 8/2009

WO 2010092795 A1 8/2010

WO 2012087977 A1 6/2012

## (56)

## References Cited

## U.S. PATENT DOCUMENTS

6,830,855 B2 12/2004 Kiguchi et al.

6,992,326 B1 1/2006 Macpherson et al.

7,132,788 B2 11/2006 Gupta et al.

7,378,790 B2 5/2008 Aruga et al.

7,443,093 B2 10/2008 Jianpu et al.

8,110,825 B2 2/2012 Obata et al.

8,115,216 B2 2/2012 Smith et al.

8,124,172 B2 2/2012 Lang et al.

8,309,376 B2 11/2012 Lang et al.

8,330,352 B2 12/2012 Sung et al.

8,405,100 B2 3/2013 Matsumoto et al.

8,790,745 B2 7/2014 Kiguchi et al.

9,444,050 B2 9/2016 Madigan

9,614,191 B2 \* 4/2017 Madigan ..... H01L 51/56

2003/0129299 A1 7/2003 Swanson

2004/0144975 A1 7/2004 Seki et al.

2005/0100657 A1 5/2005 MacPherson et al.

2005/0112341 A1 5/2005 Ito et al.

2005/0218807 A1 10/2005 Min

2005/0285509 A1 \* 12/2005 Funamoto ..... H01L 51/5209

313/504

2006/0087228 A1 4/2006 Kobayashi

2006/0164010 A1 7/2006 Hwang et al.

2006/0170354 A1 8/2006 Hwang

2008/0024402 A1 1/2008 Nishikawa et al.

2008/0111474 A1 5/2008 Sung et al.

2009/0195144 A1 \* 8/2009 Kitabayashi ..... H01L 27/3246

313/503

2009/0243483 A1 10/2009 Yang

2010/0019235 A1 1/2010 Iizumi et al.

2010/0194269 A1 8/2010 Sonoda et al.

2011/0127502 A1 6/2011 Kim

2011/0127507 A1 6/2011 Choi et al.

2011/0183268 A1 7/2011 Lang et al.

2011/0229994 A1 9/2011 Jung

2011/0309389 A1 12/2011 Yu et al.

2012/0049178 A1 3/2012 Sugimoto et al.

2012/0091482 A1 4/2012 Uchida et al.

2012/0119201 A1 5/2012 Ueno et al.

2012/0187389 A1 7/2012 Shoda et al.

2012/0228602 A1 9/2012 Nakatani et al.

2012/0319089 A1 12/2012 Shin et al.

2012/0326136 A1 12/2012 Chen

2012/0326600 A1 12/2012 Heeks et al.

2013/0109117 A1 5/2013 Lee et al.

2013/0248867 A1 9/2013 Kim et al.

2014/0070175 A1 3/2014 Kang

## OTHER PUBLICATIONS

Applicant Interview Summary dated Sep. 24, 2016, to U.S. Appl. No. 14/030,776.

Corrected Notice of Allowability dated Jan. 20, 2017, to U.S. Appl. No. 14/030,776.

Examination Report dated Dec. 19, 2016 to TW Patent Application No. 102140259.

Extended European Search Report dated Nov. 2, 2016 for EP 147403232.

Extended European Search Report dated Oct. 19, 2016 for EP Application No. 13872170.9.

Final Office Action dated Dec. 31, 2015, to U.S. Appl. No. 14/030,776.

First Office Action dated Sep. 1, 2016 for CN 2014800164841.

International Search Report and Written Opinion dated Feb. 24, 2014, to PCT Application PCT/US13/60687.

International Search Report and Written Opinion dated May 13, 2014 to PCT Application No. PCT/US2014/11723.

JP Office action dated Jan. 26, 2017, to JP Patent Application No. 2015-553715.

Non-Final Office Action dated Jun. 16, 2016 for U.S. Appl. No. 14/030,776.

Non-Final Office Action dated Jan. 4, 2016, to U.S. Appl. No. 14/156,188.

Non-Final Office Action dated May 22, 2015 to U.S. Appl. No. 14/030,776.

Notice of Allowance dated Jul. 14, 2016 for U.S. Appl. No. 14/156,188

Notice of Allowance dated Oct. 27, 2016 for U.S. Appl. No. 14/030,776.

Reid Chesterfield et al. "Solution-Coating Technology for AMOLED Displays", Frontline Technology, Information Display 1/11, pp. 24-29.

Examination Report dated Nov. 11, 2016, to TW Patent Application No. 103101751.

Notice of Allowability dated Apr. 20, 2017, to U.S. Appl. No. 15/254,562.

Notice of Allowance dated Jan. 25, 2017 for U.S. Appl. No. 15/254,562.

Office Action dated Feb. 4, 2017, to CN Patent Application No. 201380070779.8.

Non-Final Office action dated Sep. 21, 2017, to U.S. Appl. No. 15/462,651.

Penultimate Office Action dated Oct. 26, 2017, to JP Patent Application No. 2015-553715.

| (56) | References Cited                                                                             |                                                                                                                     |

|------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|      | OTHER PUBLICATIONS                                                                           |                                                                                                                     |

|      | Provisional Rejection dated Aug. 22, 2017, to KR Patent Application 10-2015-7018822.         | Examination report dated Jun. 4, 2018, to TW Patent Application No. 106117187.                                      |

|      | Provisional Rejection dated Aug. 25, 2017, to KR Patent Application No. 10-2015-7021869.     | Office action dated Aug. 1, 2018, to JP Patent Application No. 2015-553806.                                         |

|      | Second Office action dated Aug. 22, 2017, to CN Patent Application No. 201380070779.8.       | Final office action and Denial of Entry of Amendment dated Sep. 28, 2018, to JP Patent Application No. 2015-553715. |

|      | Second Office Action dated Jul. 3, 2017, to CN Patent Application No. 201480016484.7.        | Fourth Office action dated Sep. 4, 2018, to CN Patent Application 201480016484.7.                                   |

|      | Third Office action dated Oct. 23, 2017, to CN Patent Application 201480016484.7.            | Notice of Allowance dated Sep. 13, 2018, to U.S. Appl. No. 15/462,651.                                              |

|      | Office Action dated Aug. 8, 2017, to JP Patent Application No. 2015-553806.                  | Decision on Rejection dated Sep. 28, 2018, to TW Patent Application No. 106117187.                                  |

|      | Notice of Final Rejection dated Apr. 27, 2018, to KR Patent Application No. 10-2015-7018822. | Notice of Allowance dated Nov. 2, 2018, to U.S. Appl. No. 15/462,651.                                               |

|      | Notice of Allowance dated Apr. 18, 2018, to U.S. Appl. No. 15/462,651.                       | Office action dated Feb. 12, 2019, to JP Patent Application No. 2018-20895.                                         |

|      |                                                                                              | Provisional Rejection dated Feb. 13, 2019, to KR Patent Application No. 10-2018-7033172.                            |

|      |                                                                                              | * cited by examiner                                                                                                 |

FIG. 1

FIG. 3A

FIG. 3B

FIG. 4

FIG. 5A

FIG. 5B

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

# HIGH RESOLUTION ORGANIC LIGHT-EMITTING DIODE DEVICES, DISPLAYS, AND RELATED METHODS

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation case of U.S. patent application Ser. No. 14/030,776, filed Sep. 18, 2013. U.S. Ser. No. 14/030,776 claims the benefit U.S. Provisional Patent Application No. 61/753,692, filed Jan. 17, 2013, which is incorporated by reference herein in its entirety.

## TECHNICAL FIELD

Aspects of the present disclosure generally relate to electronic displays and methods for making electronic displays. More particularly, aspects of the present disclosure relate to depositing organic light-emissive layers on a substrate so as to fabricate high resolution displays.

## INTRODUCTION

The section headings used herein are for organizational purposes only and are not to be construed as limiting the subject matter described in any way.

Electronic displays are present in many differing kinds of electronic equipment such as, for example, television screens, computer monitors, cell phones, smart phones, tablets, handheld game consoles, etc. One type of electronic display relies on organic light emitting diode (OLED) technology. OLED technology utilizes an organic light-emissive layer sandwiched between two electrodes disposed on a substrate. A voltage can be applied across the electrodes causing charge carriers to be excited and injected into the organic light-emissive layer. Light emission can occur through photoemission as the charge carriers relax back to normal energy states. OLED technology can provide displays with a relatively high contrast ratio because each pixel can be individually addressed to produce light emission only within the addressed pixel. OLED displays also can offer a wide viewing angle due to the emissive nature of the pixels. Power efficiency of an OLED display can be improved over other display technologies because an OLED pixel only consumes power when directly driven. Additionally, the panels that are produced can be much thinner than in other display technologies due to the light-generating nature of the technology eliminating the need for light sources within the display itself and the thin device structure. OLED displays also can be fabricated to be flexible and bendable due to the compliant nature of the active OLED layers.

Inkjet printing is a technique that can be utilized in OLED manufacturing, and may reduce manufacturing cost. Inkjet printing uses droplets of ink containing OLED layer material and one or more carrier liquids ejected from a nozzle at a high speed to produce one or more active OLED layers including, for example a hole injection layer, a hole transport layer, an electron blocking layer, an organic light emissive layer, an electron transport layer, an electron injecting layer, and a hole blocking layer.

To form sub-pixels and prevent OLED ink from spreading between defined sub-pixels, confinement structures such as banks are provided on the substrate to define confinement wells. Inkjet printing methods can require substantial precision. In particular, as pixel density increases, the confinement areas of the confinement wells are reduced and small errors in droplet placement can cause the droplet to be

deposited outside the intended well. Moreover, droplet volumes can be too large with respect to the confinement well and droplets can undesirably spill over into adjacent sub-pixels. In addition, non-uniformities can form at the edges of the confinement wells due to film drying imperfections. As the confinement well area is reduced, the non-uniformities can encroach on the active emission area of the pixel creating undesirable visual artifacts in the light emission from the pixel caused by the non-uniformities. In addition, the ratio of the active area to the total area, both the active and non-active areas, of each pixel (referred to as the "fill factor") is reduced due to the confinement structures which in turn can reduce the lifetime of the display because each pixel has to be driven using more current to achieve equivalent display brightness levels and using more current to drive each pixel is known to reduce the pixel lifetime.

Although traditional inkjet methods address some of the challenges associated with OLED manufacturing, there exists a continued need for improvement. For example, there exists a continued need to reduce the sensitivity of the OLED manufacturing process to the droplet placement precision, in particular for OLED displays having a high resolution (i.e., high pixel density). Moreover, there exists a need to reduce undesirable visual artifacts created by the deposition of the organic light-emissive layer in high resolution displays. There also exists a need to improve the device lifetime by improving the fill factor of each pixel such that the area associated with active elements is increased. Further, there exists a need for improvement in using and manufacturing OLED displays in high resolution display applications, including but not limited to, for example, high resolution mobile phones and tablet computers, which present challenges in achieving acceptable resolution, power efficiency, display lifetime, and manufacturing cost.

## SUMMARY

The present disclosure may solve one or more of the above-mentioned problems and/or achieve one or more of the above-mentioned desirable features. Other features and/or advantages may become apparent from the description which follows.

In accordance with an exemplary embodiment of the present disclosure, a method of manufacturing an organic-light emitting diode (OLED) display can include providing on a substrate a first electrode associated with a first sub-pixel and a second electrode associated with a second sub-pixel, wherein a gap is formed between the first electrode and the second electrode and wherein the first electrode and the second electrode are positioned in a well having boundaries defined by a confinement structure on the substrate. The method can also include depositing in the well with the electrodes positioned therein, active OLED material to form a substantially continuous layer of active OLED material that spans the boundaries of the well such that a surface of the layer of active OLED material that faces away from the substrate has a non-planar topography. The depositing can be via inkjet printing. The present disclosure also contemplates an organic light emitting diode (OLED) display made according to the above method.

In accordance with an additional exemplary embodiment of the present disclosure, an organic light-emitting diode (OLED) display can include a first electrode disposed on a substrate, wherein the first electrode is associated with a first sub-pixel; and a second electrode disposed on the substrate and spaced from the first electrode to provide a gap between

the first and second electrodes, wherein the second electrode is associated with a second sub-pixel. The display can further include a confinement structure positioned on the substrate to define boundaries of a well containing the first electrode and the second electrode; and a substantially continuous active OLED material layer that spans the boundaries of the well and is disposed over the first electrode and second electrodes, wherein a surface of the active OLED material layer that faces away from the substrate has a non-planar topography.

Additional objects and advantages will be set forth in part in the description which follows, and in part will be obvious from the description, or may be learned by practice of the present teachings. At least some of the objects and advantages of the present disclosure may be realized and attained by means of the elements and combinations particularly pointed out in the appended claims.

It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive of the invention, as claimed. It should be understood that the invention, in its broadest sense, could be practiced without having one or more features of these exemplary aspects and embodiments.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate some exemplary embodiments of the present disclosure together with the description, serve to explain certain principles. In the drawings,

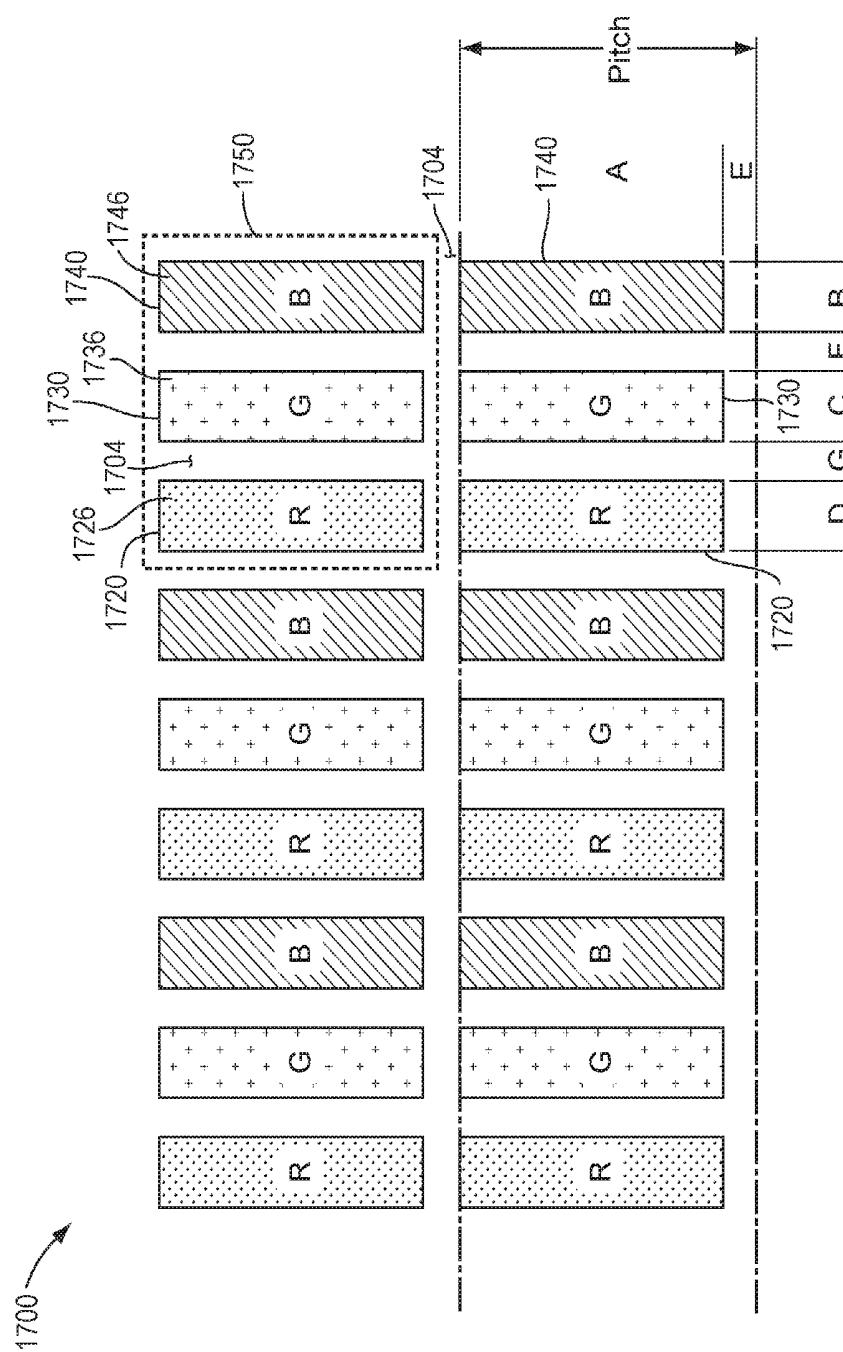

FIG. 1 is a partial plan view of a conventional pixel arrangement.

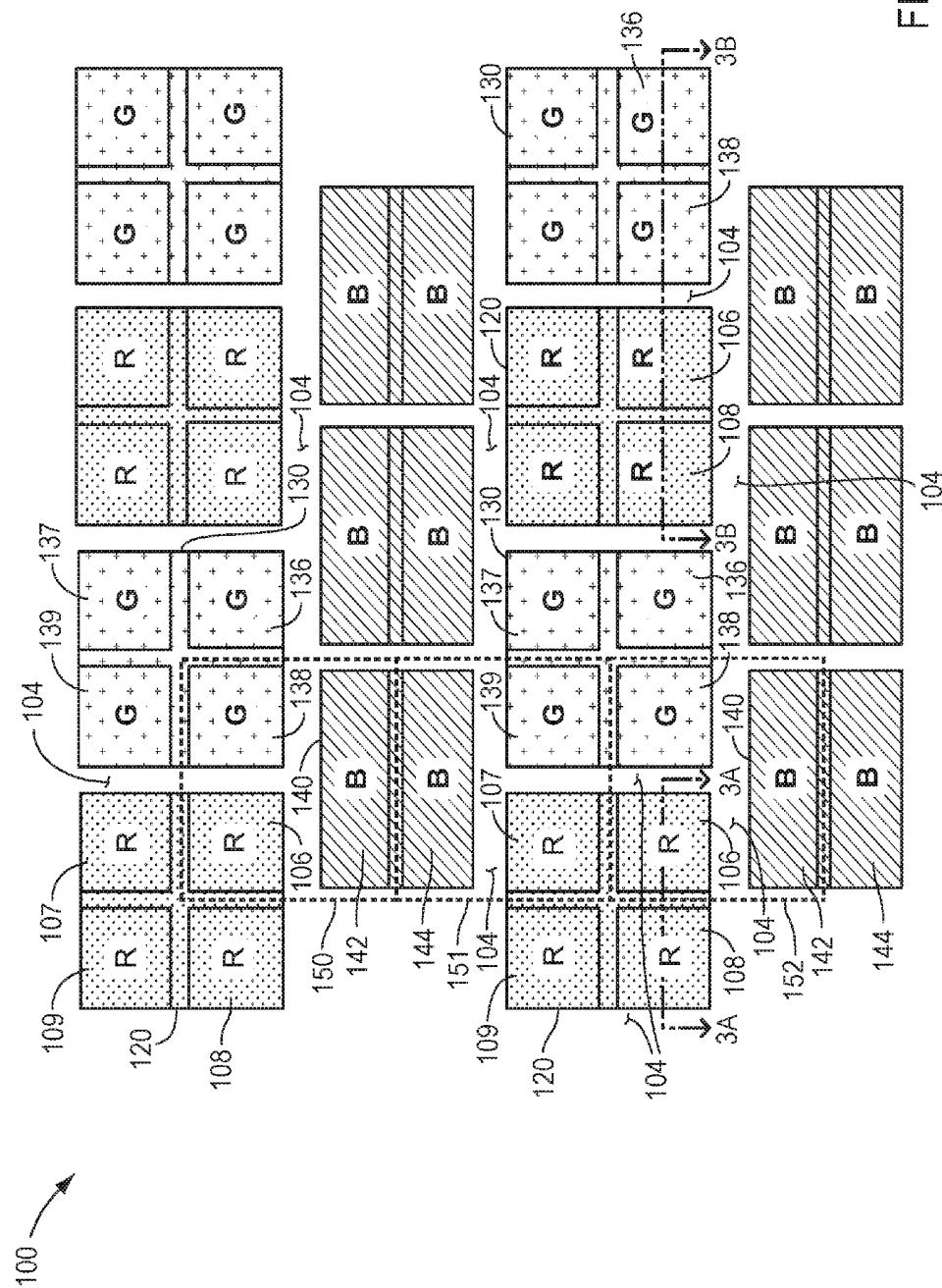

FIG. 2 is a partial plan view of an exemplary pixel arrangement in accordance with the present disclosure;

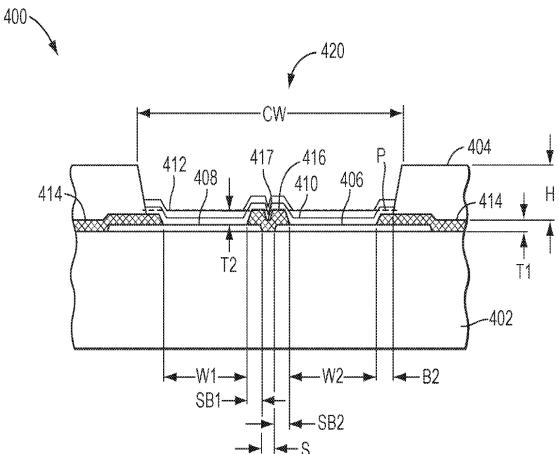

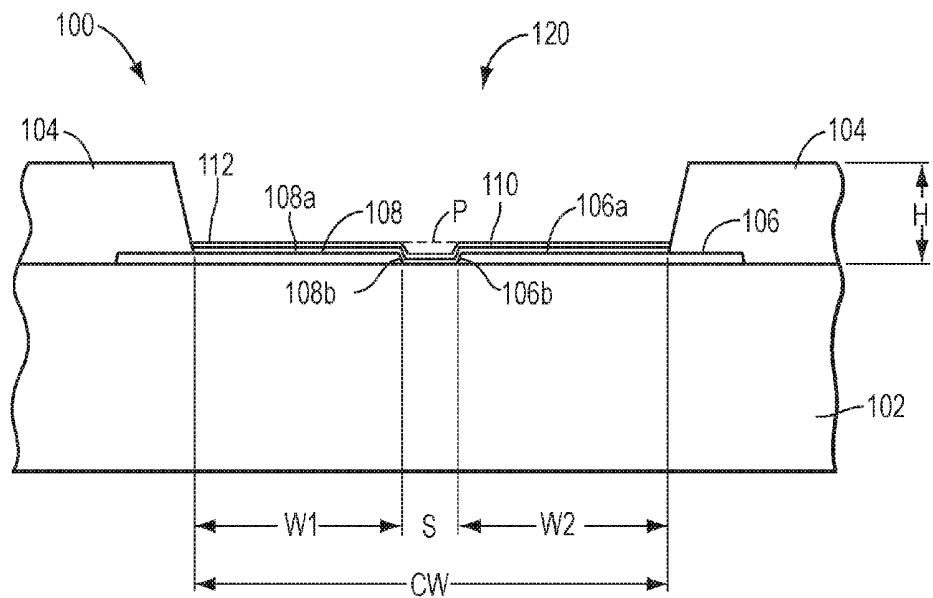

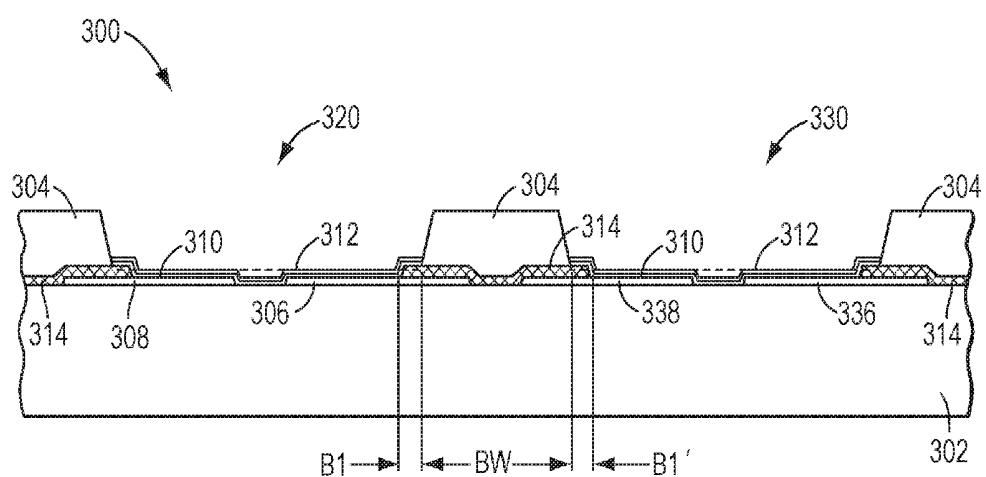

FIG. 3A is a cross-sectional view of a confinement well along line 3A-3A in FIG. 2 of an exemplary embodiment in accordance with the present disclosure;

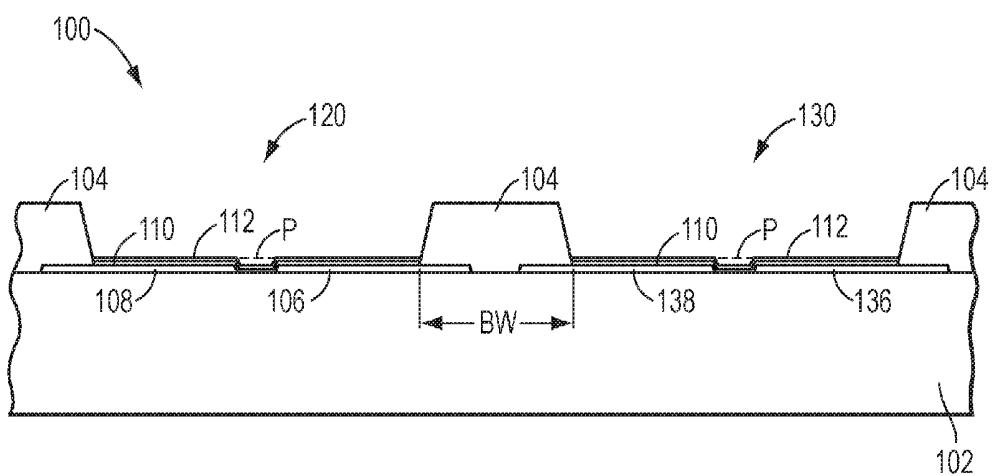

FIG. 3B is a cross-sectional view of a plurality of confinement wells along line 3B-3B in FIG. 2 of an exemplary embodiment in accordance with the present disclosure;

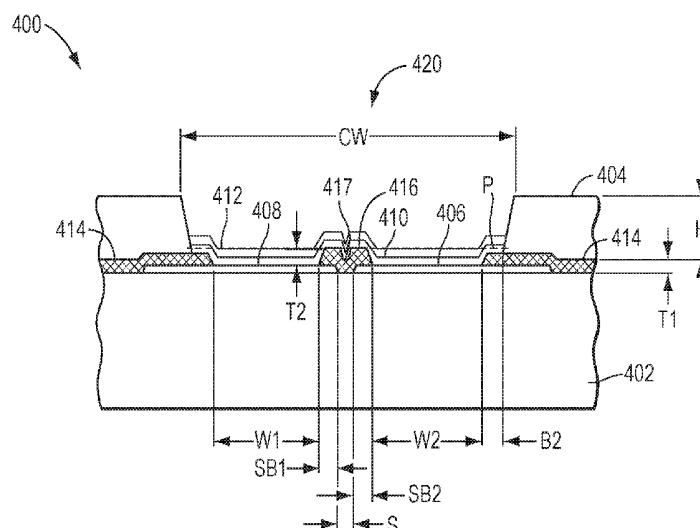

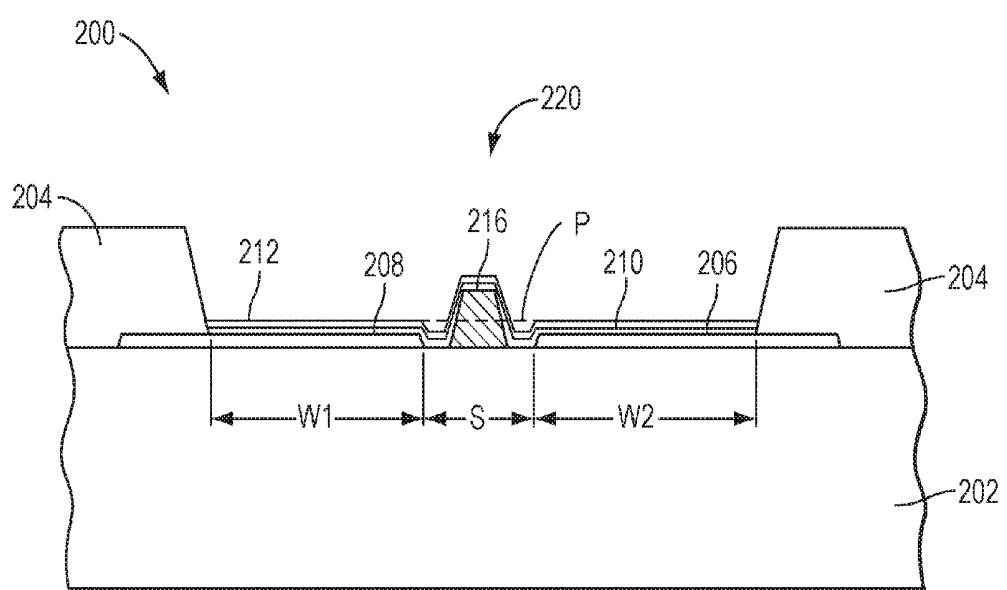

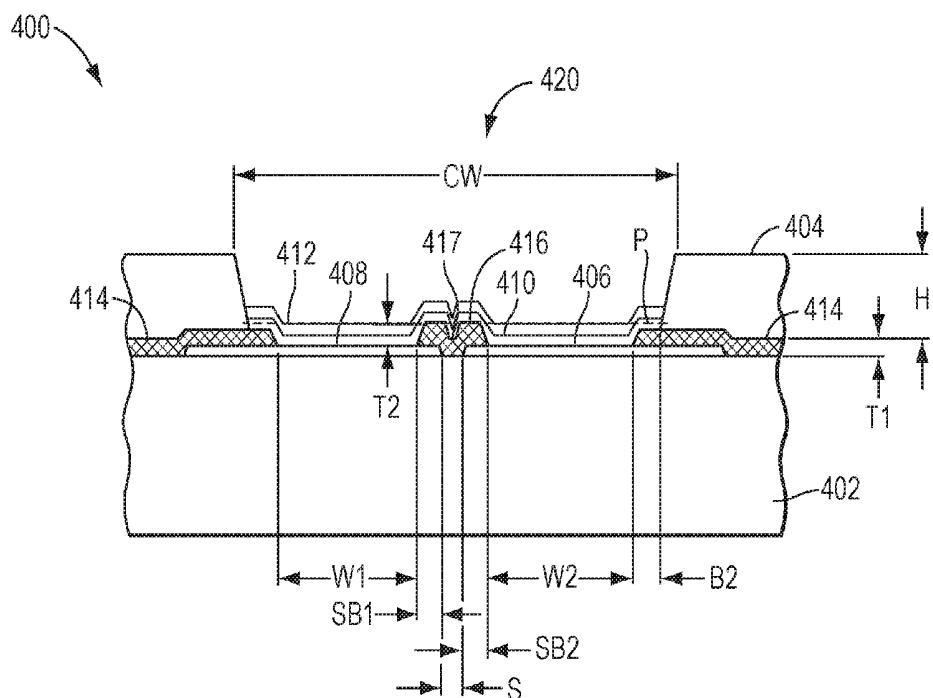

FIG. 4 is a cross-sectional view similar to the view of FIG. 3A of another exemplary embodiment of a confinement well in accordance with the present disclosure;

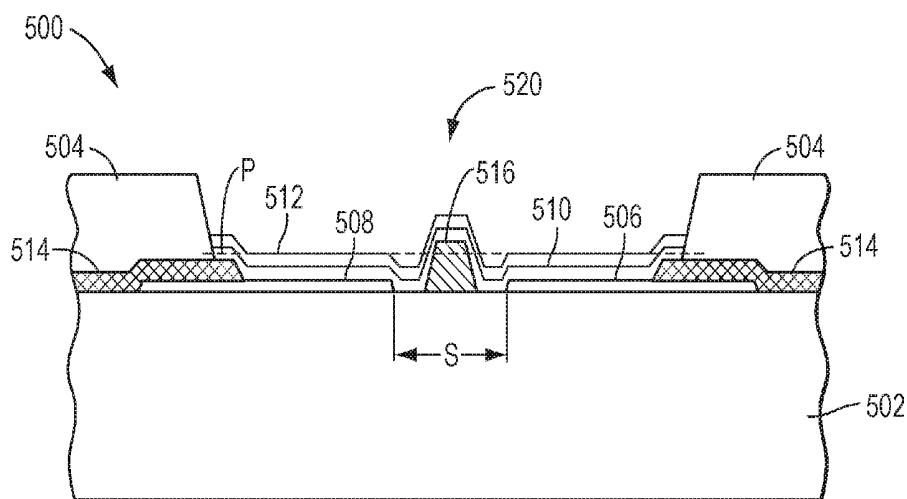

FIG. 5A is a cross-sectional view similar to the view of FIG. 3A of another exemplary embodiment of a confinement well in accordance with the present disclosure;

FIG. 5B is a cross-sectional view similar to the view of FIG. 3B of another embodiment of a confinement well in accordance with the present disclosure;

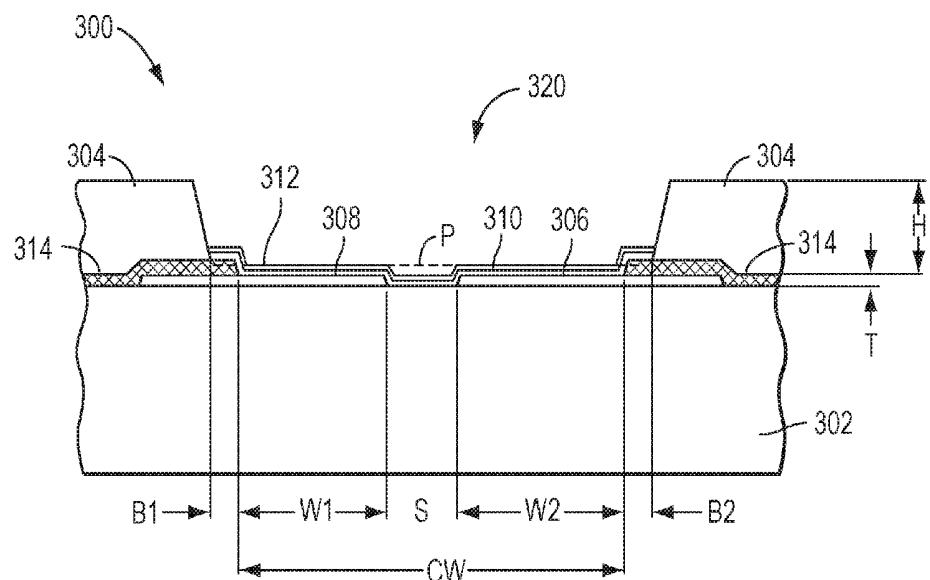

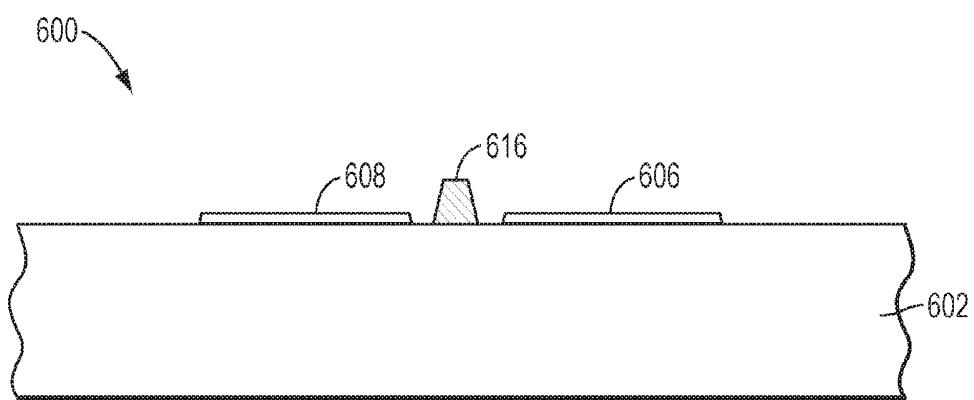

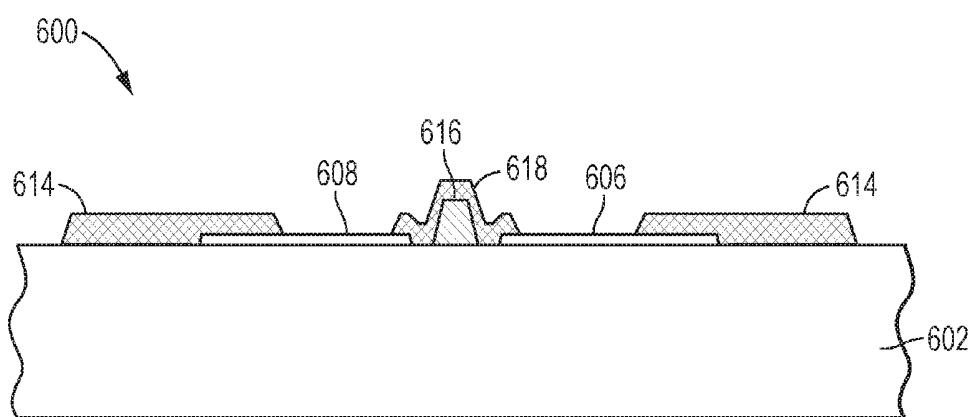

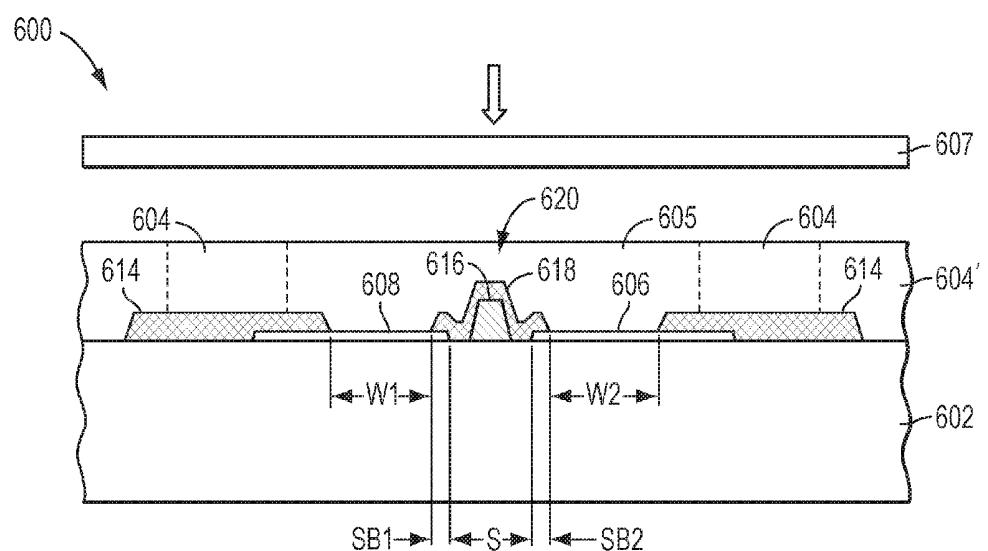

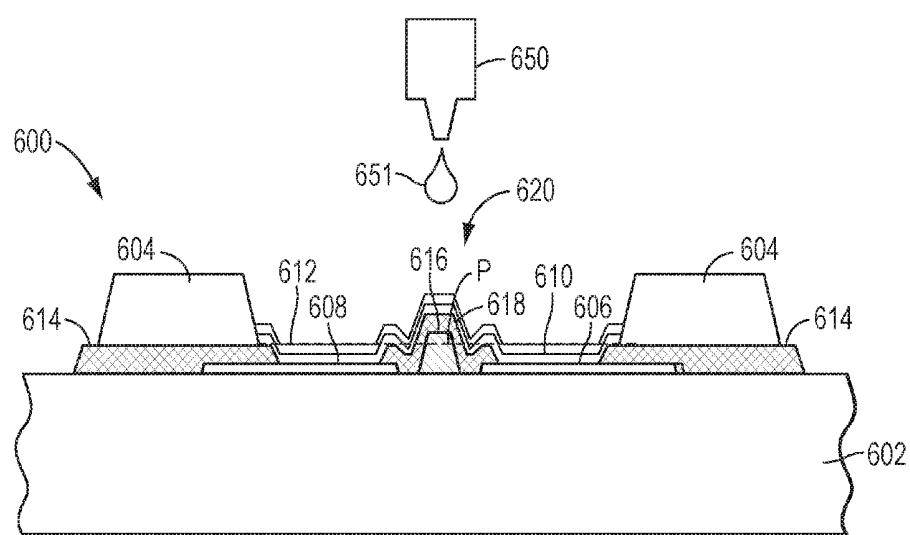

FIG. 6 is a cross-sectional view of yet another exemplary embodiment of a confinement well in accordance with the present disclosure;

FIG. 7 is a cross-sectional view of yet another exemplary embodiment of a confinement well in accordance with the present disclosure;

FIGS. 8-11 are cross-sectional views of another exemplary embodiment of a confinement well and exemplary steps for creating an OLED display in accordance with the present disclosure;

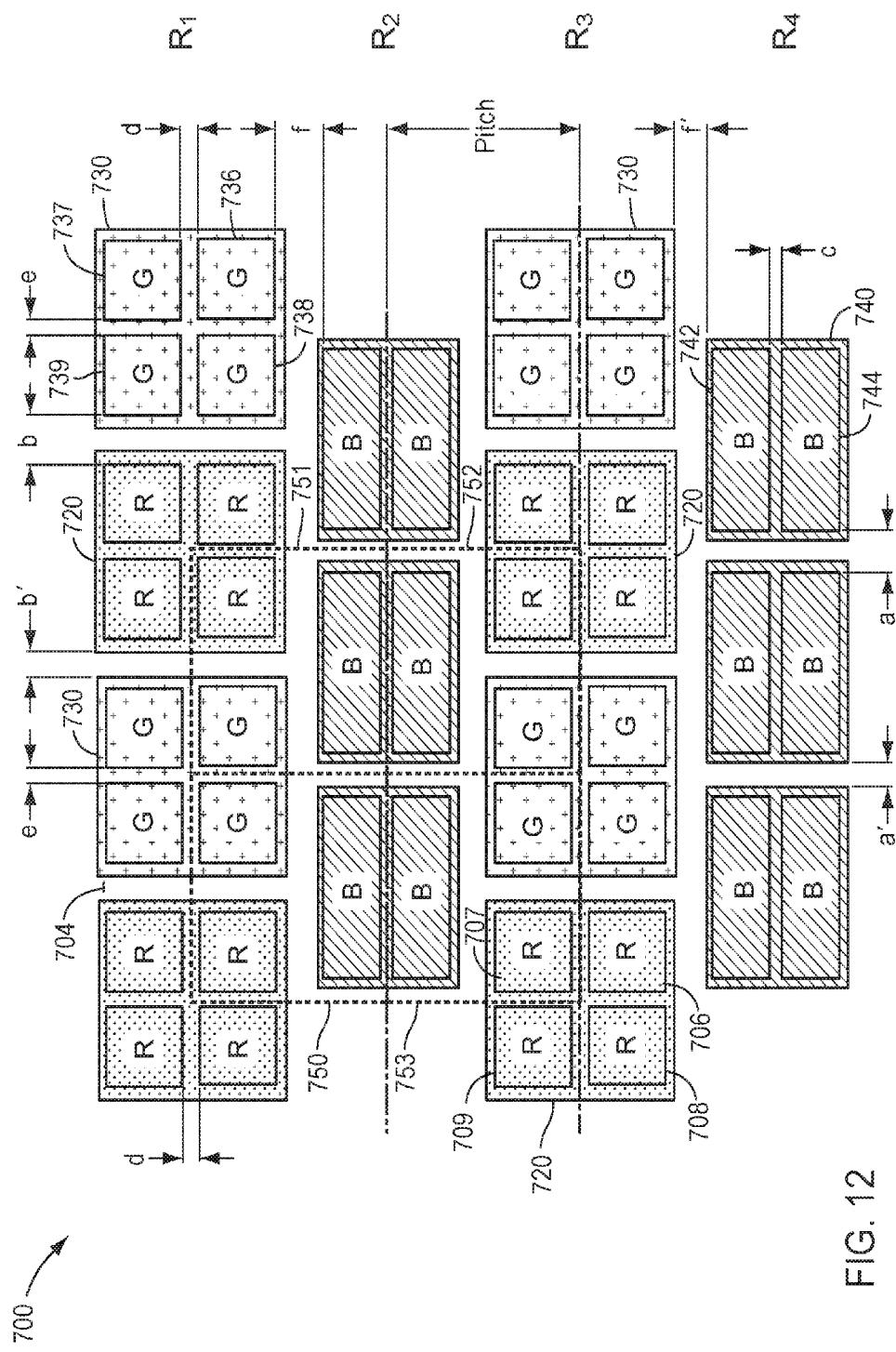

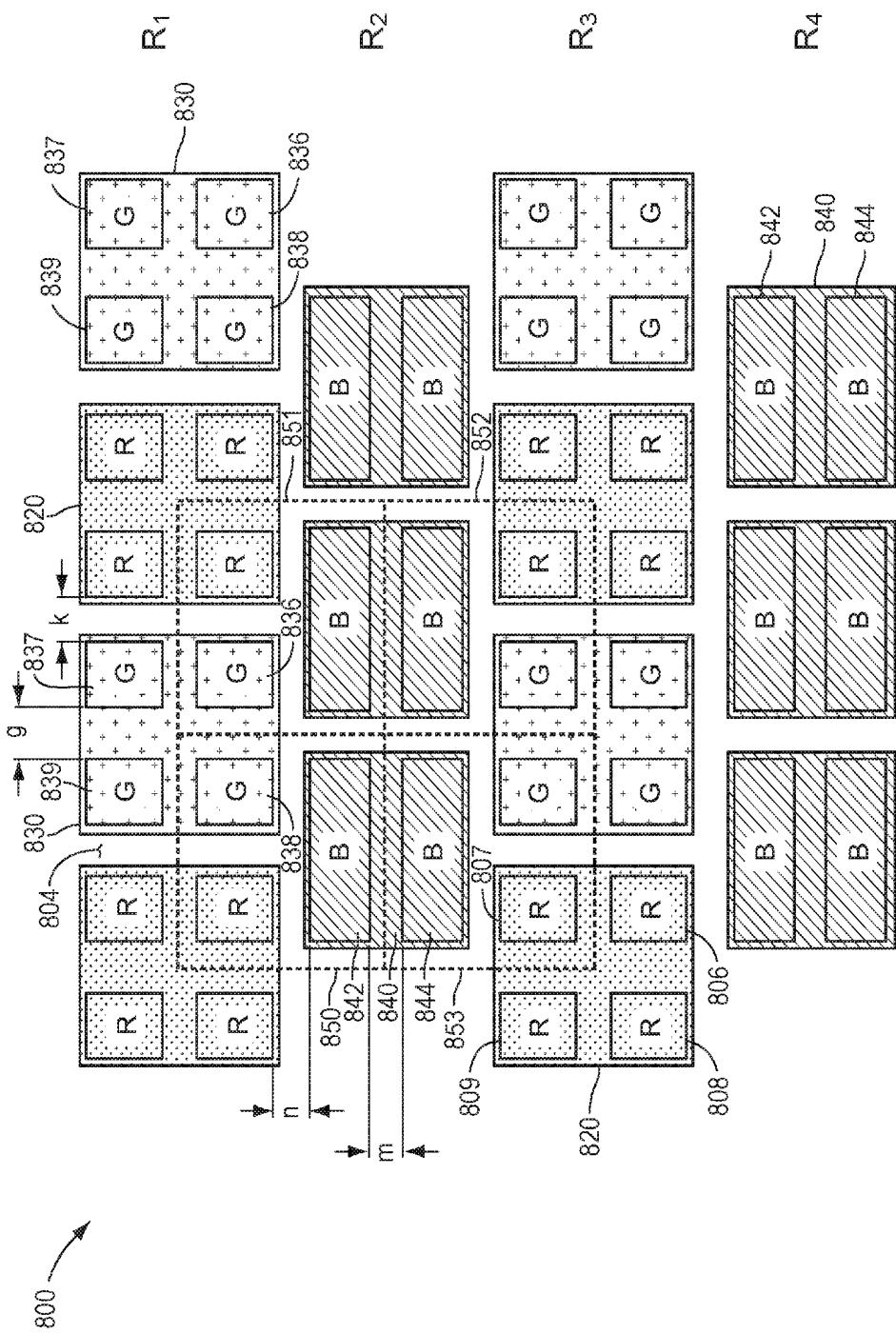

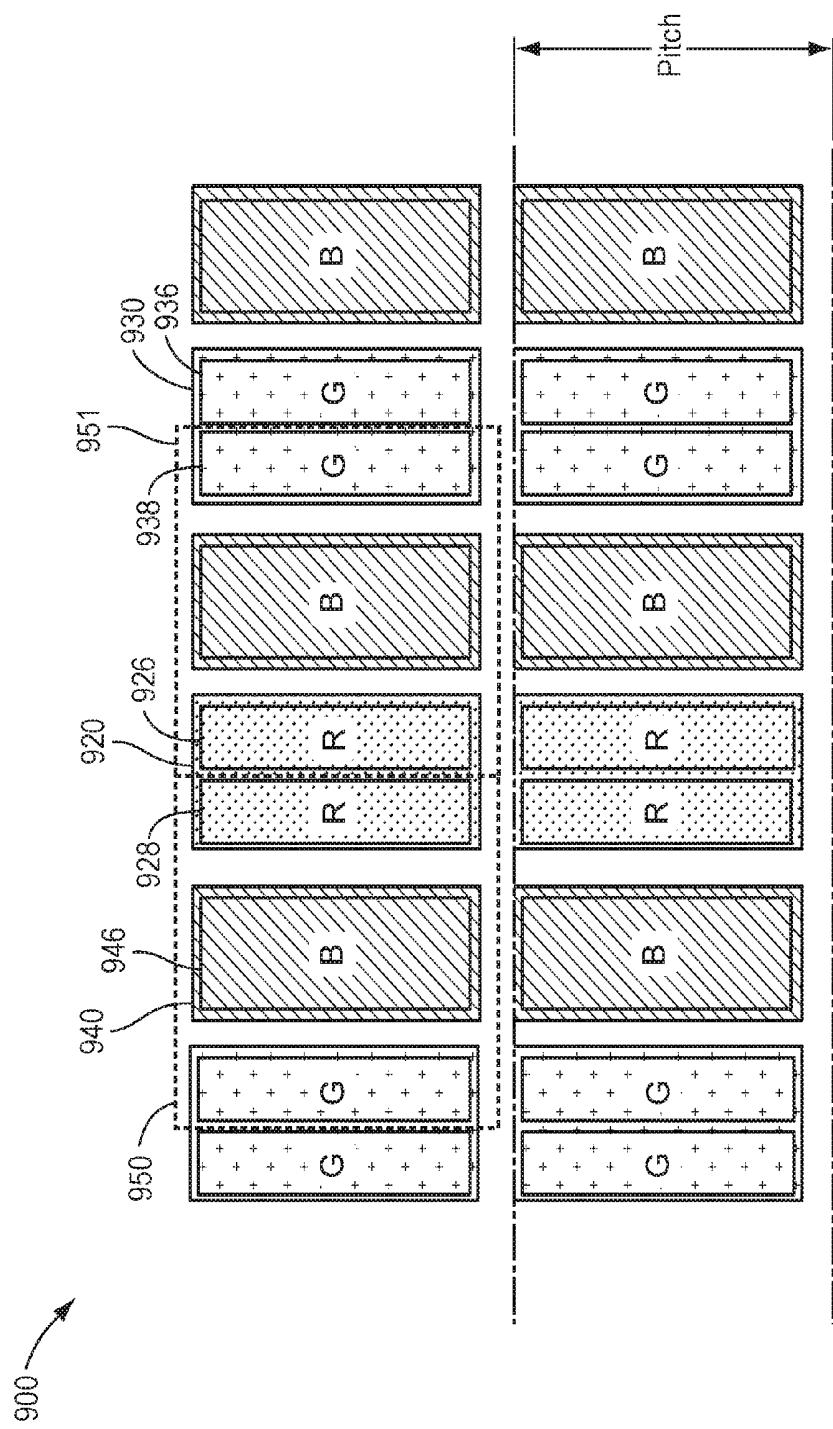

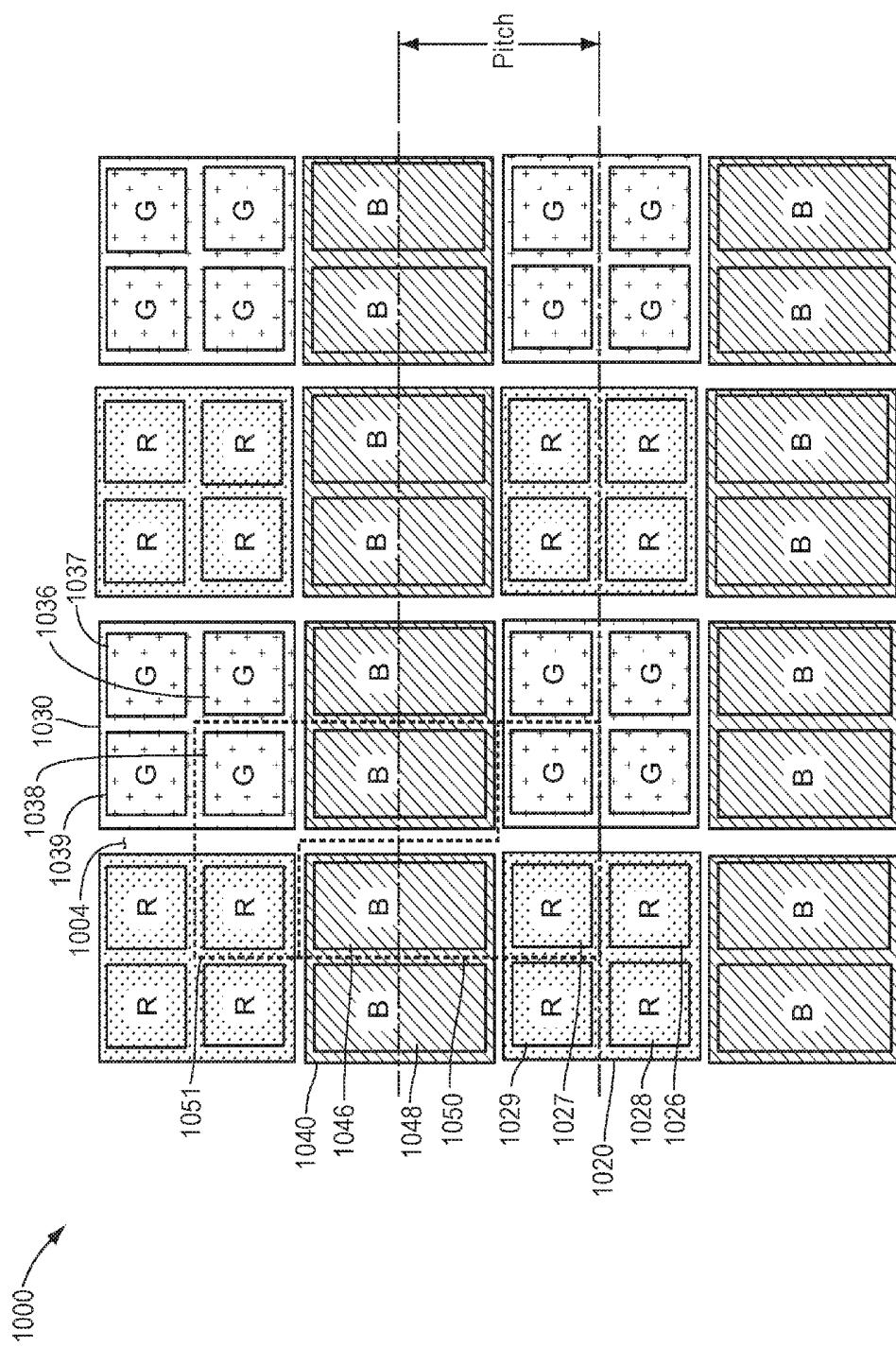

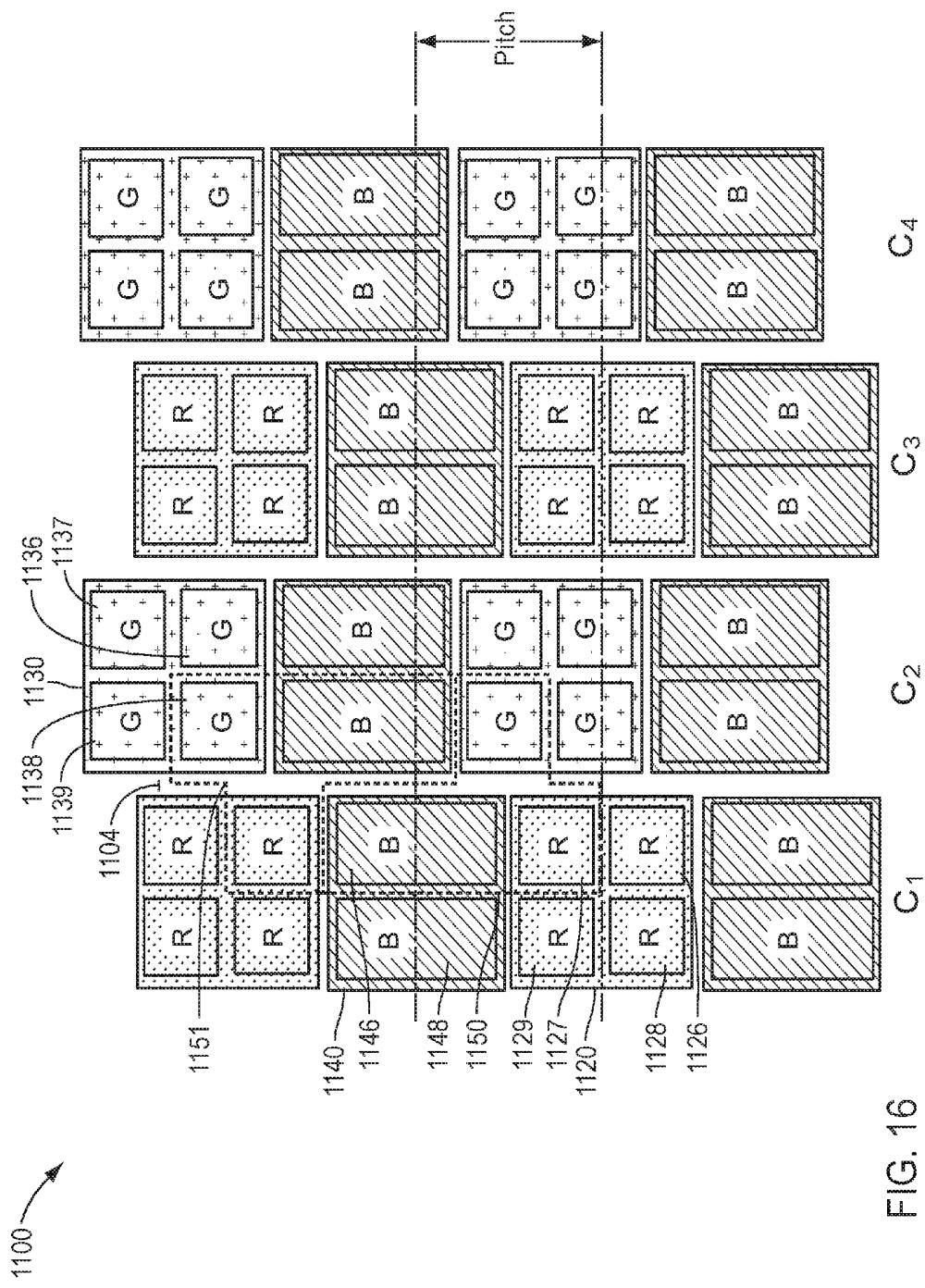

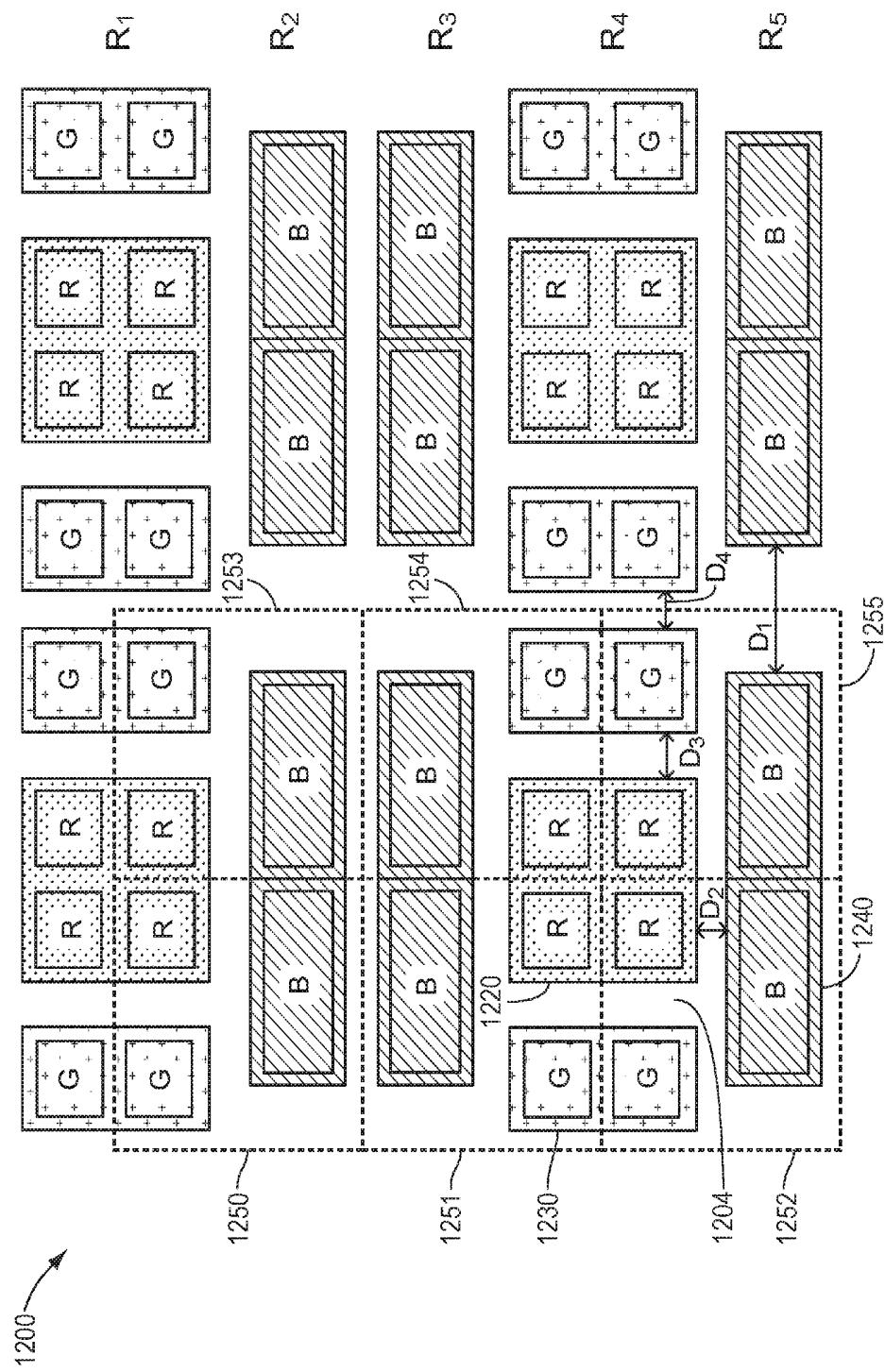

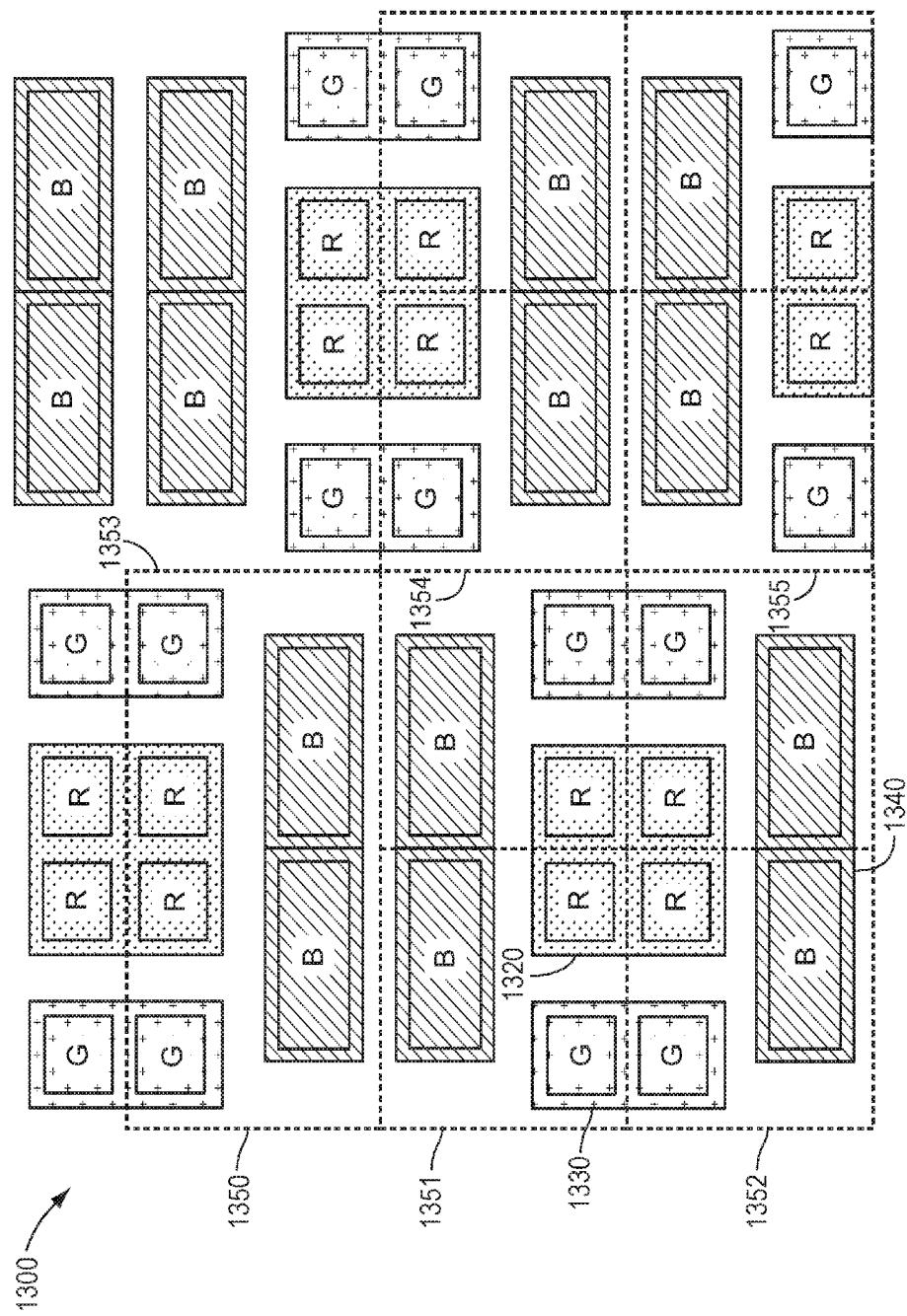

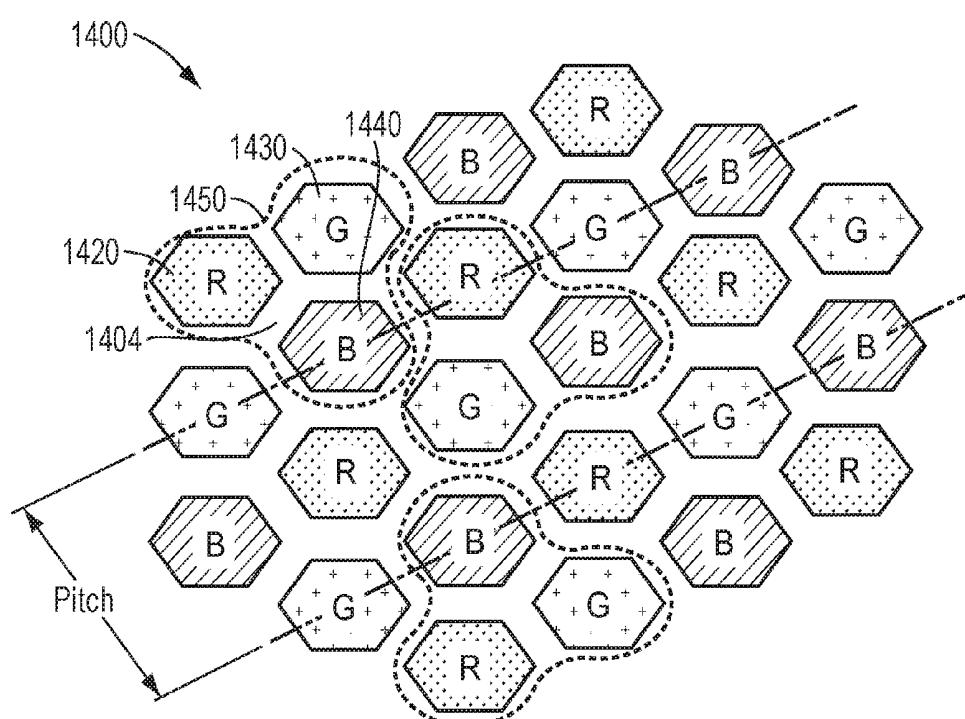

FIGS. 12-19 are partial plan views of various exemplary pixel arrangements in accordance with the present disclosure;

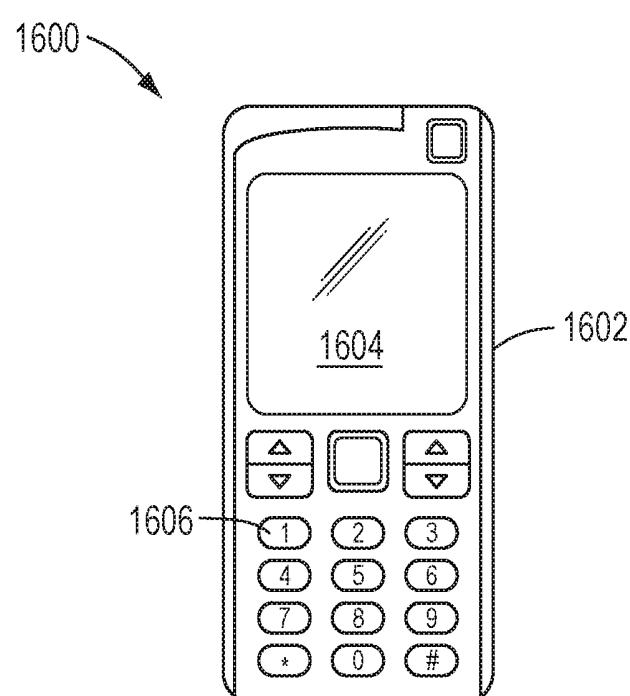

FIG. 20 is a front view of an exemplary apparatus including an electronic display in accordance with the present disclosure; and

FIG. 21 is a front view of another exemplary apparatus including an electronic display in accordance with the present disclosure.

#### DESCRIPTION OF EXEMPLARY EMBODIMENTS

Reference will now be made in detail to various exemplary embodiments of the present disclosure, examples of which are illustrated in the accompanying drawings. Whenever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

For the purposes of this specification and appended claims, unless otherwise indicated, all numbers expressing quantities, percentages, or proportions, and other numerical values used in the specification and claims, are to be understood as being modified in all instances by the term "about," to the extent they are not already so modified. Accordingly, unless indicated to the contrary, the numerical parameters set forth in the following specification and attached claims are approximations that may vary depending upon the desired properties sought to be obtained. At the very least, and not as an attempt to limit the application of the doctrine of equivalents to the scope of the claims, each numerical parameter should at least be construed in light of the number of reported significant digits and by applying ordinary rounding techniques.

It is noted that, as used in this specification and the appended claims, the singular forms "a," "an," and "the," and any singular use of any word, include plural referents unless expressly and unequivocally limited to one referent. As used herein, the term "include" and its grammatical variants are intended to be non-limiting, such that recitation of items in a list is not to the exclusion of other like items that can be substituted or added to the listed items.

Further, this description's terminology is not intended to limit the invention. For example, spatially relative terms—such as "beneath", "below", "lower", "top", "bottom", "above", "upper", "horizontal", "vertical", and the like—may be used to describe one element's or feature's relationship to another element or feature as illustrated in the figures. These spatially relative terms are intended to encompass differing positions (i.e., locations) and orientations (i.e., rotational placements) of a device in use or operation in addition to the position and orientation shown in the figures. For example, if a device in the figures is turned over, elements described as "below" or "beneath" other elements or features would then be "above" or "over" the other elements or features. Thus, the exemplary term "below" can encompass both positions and orientations of above and below depending on the overall orientation of the device. A device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein interpreted accordingly.

As used herein, "pixel" is intended to mean the smallest functionally complete and repeating unit of a light emitting pixel array. The term "sub-pixel" is intended to mean a portion of a pixel that makes up a discrete light emitting part of the pixel, but not necessarily all of the light emitting parts. For example, in a full color display, a pixel can include three primary color sub-pixels such as red, green, and blue. In a monochrome display, the terms sub-pixel and pixel are equivalent, and may be used interchangeably.

The term "coupled" when used to refer to electronic components is intended to mean a connection, linking, or association of two or more electronic components, circuits, systems, or any combination of: (1) at least one electronic

component, (2) at least one circuit, or (3) at least one system in such a way that a signal (e.g. current, voltage, or optical signal) can be transferred from one to another. The connection, linking, or association of two or more electronic components, circuits, or systems can be direct; alternatively intermediary connections, linkings, or associations may be present, and thus coupling does not necessarily require a physical connection.

One of ordinary skill in the art would generally accept the term "high resolution" to mean a resolution greater than 100 pixels per inch (ppi) where 300 ppi can sometimes be referred to as very high resolution. One of ordinary skill in the art would also recognize that pixel density does not directly correlate to the size of the display. Various exemplary embodiments disclosed herein can be used to achieve high resolution in small and large display sizes. For example, displays having a size of about 3 inches to about 11 inches can be implemented as high resolution displays. Moreover, displays having larger sizes, such as television displays up to 55" and beyond, can also be used with various exemplary embodiments described herein to achieve high resolution displays.

As used herein, a layer or structure being "on" a surface includes both the case where the layer is directly adjacent to and in direct contact with the surface over which it is formed and the case where there are intervening layers or structures between the layer or structure being formed over the surface.

Various factors can influence deposition precision of organic light-emissive layers in OLED display manufacturing techniques such factors include for example, display resolution, droplet size, target droplet area, droplet placement error, fluid properties (e.g., surface tension, viscosity, boiling point) associated with the OLED layer material (e.g., active OLED materials) inks, which are comprised of a combination of OLED layer material and one or more carrier fluids, and the velocity at which the droplets are deposited. As display resolutions increase, for example greater than 100 ppi, or for example greater than 300 ppi, various issues arise in using inkjet printing techniques for OLED display manufacturing. High precision inkjet heads used in the conventional printing techniques can produce droplet sizes ranging from about 1 picoliter (pL) to about 50 picoliters (pL), with about 10 pL being a relatively common size for high precision inkjet printing applications. Droplet placement accuracy of a conventional inkjet printing system is approximately  $\pm 10 \mu\text{m}$ . In various exemplary embodiments, confinement wells can be provided on the substrate to compensate for droplet placement errors. A confinement well can be a structure that prevents OLED material from migrating beyond a desired sub-pixel area. To ensure that a droplet accurately lands at a desired location on a substrate, such as entirely within a confinement well, various exemplary embodiments configure the confinement well to be as wide as the droplet diameter plus twice the droplet placement error of the system. For example, the diameter of a 10 pL droplet is about  $\pm 25 \mu\text{m}$  and thus the preceding parameters would indicate the use of a confinement well of at least  $45 \mu\text{m}$  ( $25 \mu\text{m} + (2 \times 10 \mu\text{m})$ ) in its smallest dimension. Even for a 1 pL droplet, the droplet diameter is  $12 \mu\text{m}$ , which indicates a confinement well of at least  $32 \mu\text{m}$  in its smallest dimension.

Various pixel layouts that rely on a confinement well of at least  $45 \mu\text{m}$  in its smallest dimension can be used in OLED displays having a resolution up to 100 ppi. However, in high resolution displays of greater than 100 ppi, for example, 10 pL droplets are too large and droplet placement accuracies too poor to reliably provide for consistent loading of drop-

lets into confinement wells around each sub-pixel. In addition, as noted above, for high resolution displays, covering an increased amount of display area with structures used to define confinement wells can negatively impact the fill factor of each pixel, where fill factor is defined as the ratio of the light emitting area of the pixel relative to the total pixel area. As fill factor decreases, each pixel must be driven harder to achieve the same overall display brightness thereby decreasing longevity and performance of each pixel of the display.

To further illustrate some of the above mentioned challenges of working with very high resolution displays, FIG. 1 illustrates one conventional pixel layout 1700. Pixel 1750 can comprise sub-pixels 1720, 1730, 1740 arranged in a side-by-side configuration, sub-pixel 1720 being associated with light emission in the red spectrum range, sub-pixel 1730 being associated with light emission in the green spectrum range, and sub-pixel 1740 being associated with light emission in the blue spectrum range. Each sub-pixel 1720, 1730, 1740 can be surrounded by confinement structures 1704 forming confinement wells directly corresponding to the sub-pixels 1720, 1730, 1740. One sub-pixel electrode can be associated with each confinement well such that electrode 1726 corresponds to sub-pixel 1720, electrode 1736 corresponds to sub-pixel 1730, and electrode 1746 corresponds to sub-pixel 1740. Sub-pixel 1720 can have a width D, sub-pixel 1730 can have a width C, and sub-pixel 1740 can have a width B, which may be the same or differ from each other. As shown, all sub-pixels can have a length A. In addition, dimensions E, F, and G can indicate the spacing between confinement well openings. Values assigned to dimensions E, F, G can be very large in some instances, e.g., greater than  $100 \mu\text{m}$ , particularly in lower resolution displays. However, for higher resolution displays, it is desirable to minimize these dimensions in order to maximize the active pixel area and thus maximize the fill factor. As illustrated in FIG. 1, the active pixel area, indicated by the shaded regions, is the entire area within each of the sub-pixel confinement wells.

Various factors can influence dimensions E, F, G, such as, for example, the minimum value for these dimensions can be restricted by the processing method. For example, in various illustrative embodiments described herein  $E=F=G=12 \mu\text{m}$  as a minimum dimension. For example, in a display having a 326 ppi resolution, the pixel pitch can be equal to  $78 \mu\text{m}$  and  $E=F=G=12 \mu\text{m}$ . The confinement wells associated with each of the sub-pixels 1720, 1730, 1740 can have a target droplet area of  $14 \mu\text{m} \times 66 \mu\text{m}$  (i.e. dimensions B  $\times$  A, C  $\times$  A, and D  $\times$  A) where  $14 \mu\text{m}$  is significantly less than the  $45 \mu\text{m}$  smallest dimension discussed above regarding using inkjet droplets having a volume of 10 pL. It is also less than the  $32 \mu\text{m}$  dimension discussed above for 1 pL droplets. In addition, the fill factor of the pixel, defined as the ratio of the active pixel area (i.e. the area associated with light emission), and the total pixel area is 46%. In other words, 54% of the pixel area corresponds to confinement structures 1704. Along the same lines, in a display having a 440 ppi resolution, the pixel pitch, P, can be equal to  $58 \mu\text{m}$  and  $E=F=G=12 \mu\text{m}$ . Confinement wells associated with each of the emitting sub-pixels 1720, 1730, 1740 can have a target droplet area of, for example,  $7 \mu\text{m} \times 46 \mu\text{m}$  where a dimension of  $7 \mu\text{m}$  is significantly less than the minimum dimensions discussed above for accurate droplet placement of both 10 pL and 1 pL inkjet droplets. In this instance, the fill factor for a display having 440 ppi is around 30%.

Deposition techniques in accordance with various exemplary embodiments described herein can provide improved reliability in loading of confinement wells and deposition of

active OLED layers for electronic displays, such as, for example, high resolution displays. Active OLED layers can include, for example, one or more of the following layers: a hole injection layer, a hole transport layer, an electron blocking layer, an organic light emissive layer, an electron transport layer, an electron injecting layer, and a hole blocking layer. Implementation of some of the above-identified active OLED layers is preferred and implementation of some active OLED layers is optional for electronic displays. For example, at least one hole conducting layer such as a hole injection layer or a hole transport layer must be present as well as an organic light emissive layer. All other above-identified layers may be included as desired to alter (e.g., improve) light emission and power efficiency of an electronic display such as an OLED display.

Various exemplary embodiments of confinement well configurations described herein can increase the size of the confinement well while maintaining high pixel resolution. For instance, various exemplary embodiments use relatively large confinement wells that span a plurality of sub-pixels, thereby enabling the use of relatively attainable droplet sizes and conventional printing system accuracies in the deposition of the active OLED layers, while also achieving relatively high pixel densities. Accordingly, inkjet nozzles that deposit droplet volumes in the range from 1 pL to 50 pL can be used, rather than requiring specially configured or reconfigured printheads with smaller droplet volumes and new printing systems, which may or may not be available. Moreover, by using such larger confinement wells, small manufacturing errors will not have a significant negative effect on deposition precision and the deposited active OLED layers can remain contained within the confinement well.

In accordance with various exemplary embodiments, inkjet printing techniques can provide sufficiently uniform deposition of active OLED layers. For example, various components typically used in OLED displays result in topographies of varying heights on the top surface layer of a confinement well, for example, heights differing by about 100 nanometers (nm) or more. For instance, components such as electrodes may be deposited on a substrate such that a gap is formed between neighboring electrodes in order to form separately addressable electrodes each associated with a differing sub-pixel. Regardless of which active OLED layers are deposited over the electrodes disposed on the substrate of the display, height differentials between the plane of the top surfaces of the electrodes and the top surface of the substrate of the display in regions between neighboring electrodes can contribute to the topography of the subsequently deposited OLED layers. Exemplary inkjet printing techniques and resulting displays in accordance with the present disclosure allow the active OLED layers to be deposited such that the thickness of the active OLED layers are sufficiently uniform, for example over the active electrode region, where active electrode regions can be regions of the electrode associated with the active sub-pixel area from which light is emitted. In an exemplary embodiment, a thickness of the OLED layer, at least over the active electrode region, can be less than the thickness of the sub-pixel electrodes. Sufficiently uniform thicknesses of the OLED layers over the active electrode area can reduce undesirable visual artifacts. For example, OLED ink formulations and printing processes can be implemented to minimize non-uniformity in the deposited film thickness within a given deposition area, even when that area includes both electrode and non-electrode regions. In other words, portions within the deposition area not covered by an electrode

structure can contribute to the OLED layer topography such that the OLED layer can sufficiently conform to the underlying structures over which it is deposited within the deposition area. Minimizing non-uniformities in the deposited film thickness can provide for substantially uniform light emission when a particular sub-pixel electrode is addressed and activated.

In accordance with yet other exemplary embodiments, pixel layout configurations contemplated by the present disclosure can increase active region areas. For example, confinement structures can define confinement wells having a contiguous area that spans a plurality of sub-pixels such that non-active portions (e.g., substrate areas associated with confinement structures) of the display are reduced. For instance, rather than a confinement structure surrounding each sub-pixel electrode as in various conventional OLED displays, a plurality of individually addressed sub-pixel electrodes can be surrounded by a confinement structure where each sub-pixel electrode can be associated with a differing pixel. By reducing the area taken up by the confinement structures, the fill factor can be maximized because the ratio of the non-active region to the active region of each pixel is increased. Achieving such increases in fill factor can enable high resolution in smaller size displays, as well as improve the lifetime of the display.

In accordance with yet other exemplary embodiments, the present disclosure contemplates an organic light-emissive display that includes a confinement structure disposed on a substrate, wherein the confinement structure defines a plurality of wells in an array configuration. The display further includes a plurality of electrodes disposed within each well and spaced apart from one another. The display further can include first, second, and third organic light emissive layers in at least one of the plurality of wells, each layer having first, second, and third light emissive wavelength ranges, respectively. A number of electrodes disposed within the well associated with the first and second organic light-emissive layer differs from a number of electrodes disposed within the well associated with the third organic light emissive layer.

In accordance with yet other exemplary embodiments, the present disclosure contemplates an organic light-emissive display that includes a confinement structure disposed on a substrate, wherein the confinement structure defines a plurality of wells in an array configuration, including a first well, a second well, and a third well. The display further can include a first plurality of electrodes disposed within the first well and associated with a differing pixel, a second plurality of electrodes disposed within the second well and associated with a differing pixel, and at least one third electrode disposed within the third well, wherein a number of electrodes disposed within each of the first and second wells differs from a number of electrodes disposed within the third well. The display can further include a first organic light emissive layer having a first light-emissive wavelength range disposed in the first well, a second organic light emissive layer having a second light-emissive wavelength range disposed in the second well, and third organic light emissive layer having a third light-emissive wavelength range disposed in the third well.

In accordance with various other exemplary embodiments, pixel layout configurations can be arranged to extend the lifetime of the device. For example, sub-pixel electrode size can be based on the corresponding organic light-emission layer wavelength range. For instance, a sub-pixel electrode associated with light emission in the blue wavelength range can be larger than a sub-pixel electrode asso-

ciated with light emission in the red or green wavelength ranges, respectively. Organic layers associated with blue light emission in OLED devices typically have shortened lifetimes relative to organic layers associated with red or green light emission. In addition, operating OLED devices to achieve a reduced brightness level increases the lifetime of the devices. By increasing the emission area of the blue sub-pixel relative to the red and green sub-pixels, respectively, in addition to driving the blue sub-pixel to achieve a relative brightness less than a brightness of the red and green sub-pixels (e.g., by adjusting the current supplied when addressing the sub-pixel as those of ordinary skill in the art are familiar with), the blue sub-pixel can serve to better balance the lifetimes of the differing colored sub-pixels while still providing for the proper overall color balance of the display. This improved balancing of lifetimes can increase the overall lifetime of the display by extending the lifetime of the blue sub-pixels.

FIG. 2 illustrates a partial, plan view of one exemplary pixel arrangement of an organic light-emitting diode (OLED) display 100 according to an exemplary embodiment of the present disclosure. FIG. 3A illustrates a cross-sectional view along section 3A-3A identified in FIG. 2 of one exemplary embodiment of a substrate, depicting various structures for forming an OLED display. FIG. 3B illustrates a cross-sectional view along section 3B-3B identified in FIG. 2 of one exemplary embodiment of a substrate, depicting various structures for forming an OLED display.

The OLED display 100 generally includes a plurality of pixels, e.g., such as defined by dotted line boundaries 150, 151, 152, that when selectively driven emit light that can create an image to be displayed to a user. In a full color display, a pixel 150, 151, 152 can include a plurality of sub-pixels of differing colors. For example, as illustrated in FIG. 2, pixel 150 can include a red sub-pixel R, a green sub-pixel G, and a blue sub-pixel B. As can be seen in the exemplary embodiment of FIG. 2, sub-pixels need not be the same size, although in an exemplary embodiment they could be. Pixels 150, 151, 152 can be defined by driving circuitry that cause light emission such that no additional structure is necessary to define a pixel. Alternatively, exemplary embodiments of the present disclosure contemplate various new arrangements of pixel definition structures that can be included within display 100 to delineate the plurality of pixels 150, 151, 152. Those having ordinary skill in the art are familiar with materials and arrangements of conventional pixel definition structures used to provide crisper delineation between pixels and sub-pixels.

With reference to FIGS. 3A and 3B in addition to FIG. 2, OLED display 100 can include a substrate 102. Substrate 102 can be any rigid or flexible structure that can include one or more layers of one or more materials. Substrate 102 can include, for example, glass, polymer, metal, ceramic, or combinations thereof. While not illustrated for simplicity, substrate 102 can include additional electronic components, circuits, or conductive members, with which those having ordinary skill in the art have familiarity. For instance, thin-film transistors (TFTs) (not shown) can be formed on the substrate before depositing any of the other structures that are discussed in further detail below. TFTs can include, for example, at least one of a thin film of an active semiconductor layer, a dielectric layer, and a metallic contact where those of ordinary skill in the art would be familiar with materials used in the manufacture of such TFTs. Any of the active OLED layers can be deposited to conform to any topography created by TFTs or other structures formed on substrate 102, as discussed below.

Confinement structures 104 can be disposed on the substrate 102 such that the confinement structures 104 define a plurality of confinement wells. For instance, the confinement structures 104 can be a bank structure. A plurality of sub-pixels can be associated with each confinement well and the organic light-emissive material deposited within each confinement well allows all sub-pixels associated with the confinement well to have the same light emission color. For example, in the arrangement of FIG. 2, confinement well 120 can receive droplets of OLED ink associated with sub-pixels that emit red light denoted by R, confinement well 130 can receive droplets of OLED ink associated with sub-pixels that emit green light denoted by G, and confinement well 140 can receive droplets of OLED ink associated with sub-pixels that emit blue light denoted by B. Those having ordinary skill in the art would appreciate, as will be further explained below, that the confinement wells can also receive various other active OLED layers, including but not limited to, for example, additional organic light-emissive material and a hole conducting layer.

The confinement structures 104 can define confinement wells 120, 130, 140 to confine material associated with a plurality of sub-pixels. In addition, confinement structures 104 can prevent spreading of OLED ink into adjacent wells, and/or can assist (through appropriate geometry and surface chemistry) in the loading and drying process such that the deposited film is continuous within the region bounded by confinement structures 104. For example, edges of the deposited films can contact the confinement structures 104 that surround the confinement wells 120, 130, 140. The confinement structures 104 can be a single structure or can be composed of a plurality of separate structures that form the confinement structures 104.

The confinement structures 104 can be formed of various materials such as, for example, photoresist materials such as photoimageable polymers or photosensitive silicone dielectrics. The confinement structures 104 can comprise one or more organic components that are, after processing, substantially inert to the corrosive action of OLED inks, have low outgassing, have a shallow (e.g. <25 degrees) sidewall slope at the confinement well edge, and/or have high photobility towards one or more of the OLED inks to be deposited into the confinement well, and may be chosen based on the desired application. Examples of suitable materials include, but are not limited to PMMA (poly-methylmethacrylate), PMGI (poly-methylglutarimide), DNQ-Novolacs (combinations of the chemical diazonaphthoquinone with different phenol formaldehyde resins), SU-8 resists (a line of widely used, proprietary epoxy based resists manufactured by MicroChem Corp.), fluorinated variations of conventional photoresists and/or any of the aforementioned materials listed herein, and organo-silicone resists, each of which can be further combined with each other or with one or more additives to further tune the desired characteristics of the confinement structures 104.

Confinement structures 104 can define confinement wells that have any shape, configuration, or arrangement. For example, the confinement wells 120, 130, 140 can have any shape such as rectangular, square, circular, hexagonal, etc. Confinement wells in a single display substrate can have the same shape and/or size or differing shapes and/or sizes. Confinement wells associated with differing light emission colors can have differing or the same shapes and/or sizes. Moreover, adjacent confinement wells can be associated with alternating light emission colors or adjacent confinement wells can be associated with the same light emission colors. In addition, confinement wells can be arranged in

columns and/or rows where the columns and/or rows can have uniform or non-uniform alignment.

The confinement wells can be formed using any of a variety of manufacturing methods, such as, for example, inkjet printing, nozzle printing, slit coating, spin coating, spray coating, screen printing, vacuum thermal evaporation, sputtering (or other physical vapor deposition method), chemical vapor deposition, etc. and any additional patterning not otherwise achieved during the deposition technique can be achieved by using shadow masking, one or more photolithography steps (e.g. photoresist coating, exposure, development, and stripping), wet etching, dry etching, lift-off, etc.

As illustrated in FIG. 2, confinement wells 120, 130, 140 according to various exemplary embodiments, can be defined by the confinement structures 104 such that they span a plurality of pixels 150, 151, 152. For example, pixel 150 includes a red sub-pixel R, a green sub-pixel G, and a blue sub-pixel B that are each part of a differing confinement well 120, 130, 140. Each confinement well 120, 130, 140 can include a plurality of electrodes, such as 106, 107, 108, 109, 136, 137, 138, 139, 142, 144, wherein the electrodes within the confinement wells 120, 130, 140 can be spaced apart from each other such that a gap S is formed between adjacent electrodes within a confinement well. In exemplary embodiments, the gap S can be of sufficient size to electrically isolate an electrode from any adjacent electrode, and in particular, the active electrode regions of adjacent electrodes can be isolated from one another. The gap or space S can reduce current leakage and improve sub-pixel definition and overall pixel definition.

While omitted for clarity and ease of illustration, drive circuitry can be disposed on the substrate 102, and such circuitry can be disposed either beneath the active pixel areas (i.e., the light emitting regions) or within the non-active pixel areas (i.e., the non-light emitting regions). In addition, while not illustrated, circuitry can also be disposed under confinement structures 104. The drive circuitry can be coupled to each electrode such that each electrode can be selectively addressed independently of the other electrodes within the confinement well. The region of non-uniform topography that results due to the gap S between electrodes is described in further detail below.

Each electrode 106, 107, 108, 109, 136, 137, 138, 139, 142, 144 within a confinement well 120, 130, 140 can be associated with a differing sub-pixel. For example, as illustrated in FIG. 2, confinement well 120 can be associated with red light emission. Electrodes 106, 107, 108, 109 can be positioned within the confinement well 120 where each electrode is operable to address a sub-pixel of a differing pixel (e.g., pixels 151 and 152 being illustrated). At least two electrodes can be positioned within each confinement well 120, 130, 140. The number of electrodes positioned within each confinement well 120, 130, 140 can be the same or differing from other confinement wells. For example, as illustrated in FIG. 2, confinement well 140 can include two sub-pixel electrodes 142, 144 associated with blue light emission and confinement well 130 can include four sub-pixel electrodes 136, 137, 138, 139 associated with green light emission.

In an exemplary embodiment, the confinement structures 104 can be disposed on a portion of the electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144. As illustrated in FIGS. 3A and 3B, the confinement well 120 can be defined by the confinement structures 104 where the confinement structures 104 are disposed partially over a portion of electrodes 106, 108 and partially directly over substrate 102

without being over an electrode. Alternatively, the confinement structures 104 can be disposed over the substrate 102 between electrodes of adjacent confinement wells. For example, the confinement structures 104 can be disposed on substrate 102 in a space formed between electrodes associated with a differing sub-pixel emission color such that the confinement structures 104 are directly disposed on substrate 102 and are not disposed over any portion of an electrode. In such a configuration (not illustrated), the electrodes corresponding to sub-pixels can be disposed either directly adjacent to (in abutment with) the confinement structures 104 or the electrodes can be spaced apart from the confinement structures 104 such that sub-pixel definition can be achieved.

When a voltage is selectively applied to an electrode 106, 107, 108, 109, 136, 137, 138, 139, 142, 144, light emission can be generated within a sub-pixel of a pixel, such as, pixels 150, 151, 152. Electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144, can be transparent or reflective and can be formed of a conductive material such as a metal, a mixed metal, an alloy, a metal oxide, a mixed oxide, or a combination thereof. For example, in various exemplary embodiments, the electrodes may be made of indium-tin-oxide, magnesium silver, or aluminum. Electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144, can have any shape, arrangement, or configuration. For example, referring to FIG. 3A, electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144, can have a profile such that the top surface 106a, 108a can be substantially planar and parallel to the surface of the substrate 102 while the side edges 106b, 108b of the electrodes can be substantially perpendicular to or can be angled and/or rounded with respect to the surface of the substrate.

It is further noted that the active portion of the electrode, i.e. the portion associated with light emission, are those portions of the electrode which are disposed directly underneath the deposited OLED layers without any intervening insulating substrate structures between the electrode surface and the OLED layers. By way of example, again with reference to FIG. 3A, the portions of electrodes 106 and 108 that are disposed beneath confinement structures 104 are excluded from the active portion of the electrode area, whereas the remainder of the regions of electrodes 106 and 108 are included in the active portion of the electrode area.

The electrodes may be deposited in various ways, such as, by a thermal evaporation, chemical vapor deposition, or sputtering method. The patterning of the electrodes may be achieved, for example, using shadow masking or photolithography. As mentioned above, electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144 can have a thickness and be spaced apart such that a topography is formed on the substrate 102, shown best in the various cross-sectional views, such as in FIG. 3A. In an exemplary embodiment, electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144 can have a thickness ranging from 60 nm to 120 nm, though this range is nonlimiting and larger or smaller thicknesses are possible as well.

One or more active OLED layers can be provided within each confinement well 120, 130, 140 such as hole conducting layer 110 and organic light emissive layer 112 shown in FIGS. 3A and 3B. The active OLED layers can be deposited such that they can sufficiently conform to the topographies that result from thickness of and spacing between the electrodes 106, 107, 108, 109, 136, 137, 138, 139, 142, 144 within a confinement well 120, 130, 140, as well as the thickness of the respective active OLED layers. For example, the active OLED layers can be continuous within

a well and have a thickness so as to sufficiently conform and follow the resultant topography of the underlying electrode structures disposed within each confinement well.

The deposited OLED layers may therefore result in a surface topography that does not lie in a single plane parallel to the substrate and across the entire confinement well. For example, one or both of OLED layers 110, 112 can be non-planar and discontinuous in a single plane of the display (wherein the plane of the display is intended as a plane parallel to substrate 102) due to the relative depression or protrusion associated with any surface feature including electrodes disposed on substrate 102. As shown, the OLED layers 110, 112 can sufficiently conform to underlying surface feature topographies such that a top surface of the OLED layer can have a resulting topography that follows the topography of the underlying surface features. In other words, each deposited OLED layer sufficiently conforms to all underlying layers and/or surface features disposed on the substrate 102 such that those underlying layers contribute to the resulting non-planar top surface topography of the OLED layers after they are deposited. In this way, in a plane across the confinement well that is parallel to a plane of the display, a discontinuity in layer 110 or 112, or both, can arise as the layer(s) rise and/or fall, relative to the plane, with the existing surface features provided from electrodes, circuitry, pixel definition layers, etc., in the confinement well. While the active OLED layers 110 and/or 112 need not perfectly conform to the underlying surface topography (for example, as explained below there may be local non-uniformities in thickness around edge regions and the like), a sufficiently conformal coating in which there are no significant build-ups or depletions of material can promote a more even, uniform, and repeatable coating.

As shown in FIG. 3A, each layer 110, 112 can be substantially continuous within the entire confinement well 120 such that each layer is disposed over substantially all surface features within the confinement well 120 (e.g. sub-pixel electrodes, circuitry, pixel definition layers, etc.) where the edges of each layer contact the confinement structures 104 surrounding the confinement well 120. In various exemplary embodiments, active OLED layer material can be deposited to form a discrete continuous layer entirely within a confinement well to substantially prevent any discontinuities in the layer within the well (in other words a region within the well where the active OLED layer material is missing). Such discontinuities can cause undesirable visual artifacts within the emission region of a sub-pixel. It is worth noting that though each layer 110, 112 is substantially continuous within the confinement well, it can nonetheless be discontinuous in a single plane, as noted above, due to the rising/falling of the layer as it sufficiently conforms to existing topographies of features disposed in the confinement well over which the layers are deposited. For example, in exemplary embodiments, if such a rise and/or fall is by an amount, e.g., 100 nm, greater than the thickness of the thinnest part of the deposited layer within the well, e.g., 50 nm, the OLED material layer will not be continuous in a plane parallel to the display within the well.

The layers 110, 112 can have a substantially uniform thickness within each confinement well which may provide for more uniform light emission. For the purpose of this application, substantially uniform thickness can refer to an average thickness of the OLED layer over planar surface regions, such as over active electrode regions, but also can encompass minute variations or local non-uniformities in thickness as described below. Over the planar surface regions, e.g. 106a, 108a, and bottom surface of gaps in FIG.

3A, it is anticipated that for a substantially uniform OLED coating the variation in thickness from an average thickness of the OLED layer can be less than  $\pm 20\%$ , such as less than  $\pm 10\%$  or less than  $\pm 5\%$ .

As noted above, however it is contemplated that local non-uniformities in thickness may arise in portions of the layers 110, 112 surrounding changes in surface topography and/or surface chemistry, and in such regions, the film thickness can locally deviate substantially from the  $\pm 20\%$ ,  $\pm 10\%$ , or  $\pm 5\%$  parameters specified above. For example, local non-uniformities in the thickness of a continuous layer can occur due to the topography associated with surface features disposed on substrate 102 and/or a change in surface chemistry between the surface features disposed on the substrate 102 such as at the edge of the confinement well structures 104, at the edge of a pixel definition layer (discussed below), on the electrode edge sidewalls (e.g. along 106b, 108b), or where the electrode meets the substrate surface. Local non-uniformities can lead to deviations in film thickness. For example, the local non-uniformities can deviate from the thickness of the layers 110, 112 provided over the active electrode regions (e.g. along 106a, 108a) of electrodes 106, 108. The non-uniformities can create generally localized “edge effect” deviations within a range of approximately 5  $\mu\text{m}$ -10  $\mu\text{m}$  around such surface features disposed on substrate 102 in the confinement well, such as at edges of electrodes, circuitry, pixel definition layers, etc. For the purposes of this application, such “edge effect” deviations are intended to be encompassed when describing the OLED film coating as having a “substantially uniform thickness” within the well.

In an exemplary embodiment, the thickness of each layer 110, 112 can be equal to or less than the thickness of the electrodes such that the upper surface of each layer does not lie in a single plane parallel to the plane of the display (i.e., a plane parallel to the substrate) due to the dip in the film formed as the layer traverses the gap between the active regions of the electrodes. This is illustrated, for example, in FIG. 3A, wherein a dashed line is provided to illustrate a plane P that is parallel to the plane of the substrate 102. As shown, layers 110, 112 can each have an average thickness that is substantially uniform within the region of layers 110, 112 over with the active electrode regions of electrodes 106, 108. However, layers 110, 112 can also include small and localized non-uniform thickness in areas associated with topography changes caused by the surface features such as around edges of those surface features (e.g. edges of electrodes 106, 108 adjacent to the gap).

The layers 110, 112 can be deposited using any manufacturing method. In an exemplary embodiment, the hole conducting layer 110 and the organic light-emission layer 112 can be deposited using inkjet printing techniques. For example, the material of hole conducting layer 110 can be mixed with a carrier fluid to form an inkjet ink that is formulated to provide reliable and uniform loading into the confinement wells. The ink for depositing hole conducting layer 110 can be delivered to the substrate at high speeds from an inkjet head nozzle into each confinement well. In various exemplary embodiments, the same hole conducting material can be delivered to all of the confinement wells 120, 130, 140 so as to provide for depositing of the same hole conducting layer 110 within all of the confinement wells 120, 130, 140. After material is loaded into the confinement wells to form hole conducting layer 110, the display 100 can be dried to allow any carrier fluid to evaporate, a process which can include exposing the display to heat, to vacuum, or ambient condition for a set period of time. Following

drying, the display may be baked at an elevated temperature so as to treat the deposited film material, for example, to induce a chemical reaction or change in film morphology that is beneficial for the quality of the deposited film or for the overall process. The material associated with each organic light-emissive layer **112** can be similarly mixed with a carrier fluid such as an organic solvent or a mixture of solvents to form inkjet inks that are formulated to provide reliable and uniform loading into the confinement wells. These inks can then be inkjet deposited using an inkjet process within the appropriate confinement wells **120**, **130**, **140** associated with each emission color. For example, the ink associated with the red organic light-emissive layer, the ink associated with the green organic light-emissive layer, and the ink associated with the blue organic light-emissive layer are separately deposited into the corresponding confinement wells **120**, **130**, **140**. The differing organic light-emissive layers **112** can be deposited simultaneously or sequentially. After loading with one or more of the inks associated with the organic light emissive layers, the display can be similarly dried and baked as described above for the hole conducting layer.

While not illustrated, additional active OLED layers of material can be disposed within the confinement well. For example, OLED display **100** can further include a hole injection layer, a hole transport layer, an electron blocking layer, a hole blocking layer, an electron transport layer, an electron injection layer, a moisture protection layer, an encapsulation layer, etc., all of which those having ordinary skill in the art are familiar with but are not discussed in detail here.

The hole conducting layer **110** can include one or more layers of material that facilitates injection of holes into the organic light-emissive layer **112**. For example, hole conducting layer **110** can include a single layer of hole conducting material such as, for example, a hole injection layer. Alternatively, hole conducting layer **110** can include a plurality of layers such as at least one of a hole injection layer, such as Poly(3,4-ethylenedioxythiophene:poly(styrene-sulfonate)) (PEDOT:PSS), and a hole transport layer, such as N,N'-Di-((1-naphthyl)-N,N'-diphenyl)-1,1'-biphenyl)-4,4'-diamine (NPB).

The organic light-emissive layer **112** can be deposited over the hole conducting layer **110** such that organic light-emissive layer **112** sufficiently conforms to the topography created by the electrodes, the space between the electrodes, and the topography of the hole conducting layer. The organic light-emissive layer **112** can include material to facilitate light emission such as an organic electroluminescence material.

In an exemplary embodiment, the thickness of the OLED stack (e.g. all active OLED layers deposited over the electrodes within a confinement well) can range from 10 nm to 250 nm. For example, a hole transport layer can have a thickness ranging from 10 nm to 40 nm; a hole injection layer can have a thickness ranging from 60 nm to 150 nm; an organic light-emissive layer can have a thickness ranging from 30 nm-150 nm, and optionally a hole blocking layer, electron transport layer, and electron injection layer having combined thickness ranging from 10 nm to 60 nm.

In an exemplary embodiment, it is contemplated that droplets having a volume of about 10 pL or less may be used to produce each of layers **110**, **112**. In various exemplary embodiments, droplet volumes of 5 pL or less, 3 pL or less, or 2 pL or less may be used. The OLED layers **110**, **112** can be formed using from 1 to 20 droplets having the above described volumes.

In one exemplary and nonlimiting embodiment, the present disclosure contemplates confinement wells arranged such that the areas of the wells associated with red, green, or blue light emissions **120**, **130**, **140** can be 66  $\mu\text{m} \times 66 \mu\text{m}$  for displays having a resolution of 326 ppi (e.g., Pitch=78  $\mu\text{m}$ ) where the width between neighboring wells in this embodiment can be 12  $\mu\text{m}$ . The area associated with red or green sub-pixel light emission of such an arrangement can be 31.5  $\mu\text{m} \times 31.5 \mu\text{m}$ , and the area associated with blue sub-pixel light emission can be 66  $\mu\text{m} \times 30 \mu\text{m}$ , leading to an overall pixel fill factor of 65%, as compared to the fill factor of 46% for the conventional RGB side-by-side layout described with reference to FIG. 1. For another exemplary and nonlimiting embodiment, a display having a resolution of 440 ppi (e.g., Pitch=58  $\mu\text{m}$ ), it is contemplated to arrange confinement wells such that areas of the wells associated with red, green, or blue light emissions **120**, **130**, **140** can be 46  $\mu\text{m} \times 46 \mu\text{m}$ , where again the width between neighboring wells in this embodiment is 12  $\mu\text{m}$ . An area associated with red or green sub-pixel light emission of such a display structure can be 20.3  $\mu\text{m} \times 20.3 \mu\text{m}$ , while an area associated with blue sub-pixel light emission can be 76  $\mu\text{m} \times 49.1 \mu\text{m}$ , thereby producing a fill factor of approximately 46%, as compared to the fill factor of 30% for the conventional RGB side-by-side layout described with reference to FIG. 1. In these embodiments the width between adjacent wells can be 12  $\mu\text{m}$ , but as discussed above, this width can take on different values, and while a smaller value may be desirable (to provide for a greater proportion of the substrate area assigned to the active electrode areas), processing constraints on the formation of the well structure and circuit layout constraints may effectively set a lower bound on this dimension. The value of 12  $\mu\text{m}$  is selected as representative for these examples, but one having ordinary skill in the art would appreciate that other dimensions could be used, for example, larger dimensions like 20  $\mu\text{m}$ , or smaller dimensions, like 8  $\mu\text{m}$ , 6  $\mu\text{m}$ , or even 1  $\mu\text{m}$  without departing from the scope of the present disclosure and claims. One having ordinary skill in the art can further appreciate that while in the above examples, the red, green, and blue confinement wells each have identical dimensions, other arrangements are possible. For example, two confinement wells associated with differing emission colors can have the same dimensions and one confinement well associated with yet another differing emission color can have a differing dimension or the confinement wells associated with each emission color can have differing dimensions.

These exemplary, non-limiting arrangements in accordance with the present disclosure provide for confinement wells having minimum well dimensions of greater than 45  $\mu\text{m}$  even for the very high resolution case of 440 ppi, and therefore can permit droplet volumes, for example, of around 10 pL, to be used, thereby simplifying manufacturing by allowing for the use of droplet volumes that are available from existing inkjet printing. In addition, the above exemplary, non-limiting arrangements increase pixel fill factor as compared to a conventional RGB side-by-side layout by about 43% and 84% for the 326 ppi and 440 ppi cases respectively. More generally, the various exemplary embodiments in accordance with the present disclosure provide enhancements in the fill factor of high resolution displays manufactured using inkjet, such as very high resolution displays, for which enhancements of 40% or more are possible.

As those of ordinary skill in the art are familiar with, a common electrode (not shown) can be disposed over the organic light-emissive layer **112** following deposition. After

the common electrode is deposited, the resulting topography of the common electrode can sufficiently conform to topography of organic light-emissive layer 112. The common electrode can be deposited using any manufacturing technique, for example, by vacuum thermal evaporation, sputtering, chemical vapor deposition, spray coating, inkjet printing, or other techniques. The common electrode can be transparent or reflective and can be formed of a conductive material such as a metal, a mixed metal, an alloy, a metal oxide, a mixed oxide, or a combination thereof. For example, indium tin oxide or a thin layer of magnesium silver. The thickness of the common electrode can range from approximately 30 nm to 500 nm.

In addition, the common electrode can have any shape, arrangement, or configuration. For example, the common electrode can be disposed as a discrete layer associated with single sub-pixel, or a single pixel. Alternatively, the common electrode can be disposed over multiple sub-pixels or pixels, for example, over the entire pixel arrangement of the display 100. For instance, the common electrode can be blanket deposited within the confinement wells 120, 130, 140 as well as over the confinement structures 104. Additional active OLED layers (not shown for simplicity) can be deposited onto the organic light emissive layer 112 before deposition of a common electrode, such as electron transport layers, electronic injection layers, and/or hole blocking layers. Such additional OLED layers can be deposited by inkjet printing, by vacuum thermal evaporation, or by another method.

In accordance with exemplary embodiments, the OLED device 100 can have a top emissive configuration or a bottom emissive configuration. For example, as illustrated in FIG. 3A, in a top emissive configuration, electrodes 106, 108 can be reflective electrodes and the common electrode that is disposed over the organic light-emissive layer can be a transparent electrode. Alternatively, in a bottom emissive configuration, electrodes 106, 108 can be transparent and the common electrode can be reflective.

In another exemplary embodiment, the OLED display 100 can be an active-matrix OLED (AMOLED). An AMOLED display, as compared to a passive-matrix OLED (PMOLED) display, can enhance display performance, but relies on active drive circuitry, including thin film transistors (TFTs), on the substrate and such circuitry is not transparent. While PMOLED displays have some elements, such as conductive bus lines that are not transparent, AMOLED displays have substantially more elements that are non-transparent. As a result, for a bottom emission AMOLED display, the fill factor may be reduced compared to a PMOLED because light can only be emitted through the bottom of the substrate between the non-transparent circuit elements. For this reason, it may be desirable to use a top emission configuration for AMOLED displays since using such a configuration may permit the OLED device to be constructed on top of such non-transparent active circuit elements. Thus, light can be emitted through the top of the OLED device without concern for the opacity of the underlying elements. In general, using a top emission structure can increase the fill factor of each pixel 150 of display 100 because light emission is not blocked by additional non-transparent elements (e.g. TFTs, driving circuitry components, etc.) deposited on the substrate 102.

In addition, non-active areas of each pixel can be limited to the confinement structures, surface features, and/or pixel definition layers (examples of which are described in further detail below) formed on the substrate 102. A conductive grid also can be disposed on substrate 102 to prevent an unde-

sirable voltage drop across the display 100, which can arise because the transparent top electrodes used in top emission OLED structures typically have low conductivities. When the common electrode is blanket deposited within the confinement wells 120, 130, 140 and over the confinement structures 104, the conductive grid can be disposed on non-active portions of the substrate 102 and coupled to the common electrode through via holes formed in selected confinement structures 104. However, the present disclosure is not limited to a top emission active-matrix OLED configuration. The techniques and arrangements discussed herein can be used with any other type of displays such as bottom emission and/or passive displays as well as those one of ordinary skill in the art would understand how to make using appropriate modifications.

In an exemplary embodiment, as illustrated in FIG. 3A, each confinement well can include a plurality of active sub-pixel regions that span W1 and W2, respectively, and are separated by gap S, and are confined within a well having width CW. The dimensions, W1, W2, and CW are primarily related to pixel pitch, which correlates to the resolution (e.g. 326 ppi, 440 ppi) of the display. The dimension of the gap S is related to restrictions associated with fabrication techniques and processes, and layout. In general, it may be desirable to minimize the dimension associated with the gap S. For example, 3  $\mu$ m may be a minimum dimension; however, one of ordinary skill in the art would appreciate that dimensions from as small as 1  $\mu$ m to greater than 10  $\mu$ m are possible. The height H of confinement structures 104 is also related to processing restrictions rather than a particular display layout or resolution. While an exemplary value of the height H of confinement structures 104 may be 1.5  $\mu$ m, the height H, can range from 0.5  $\mu$ m to 5  $\mu$ m in various exemplary embodiments. Referring to FIG. 3B, BW is the width of the confinement structures 104 between adjacent wells (e.g., wells 120 and 130 in FIG. 3B). As described above, it may be desirable to minimize this dimension and an exemplary value is 12  $\mu$ m. However, one of ordinary skill would understand that this value can be arbitrarily large (e.g. hundreds of microns) in some instances, and can also be as small as 1  $\mu$ m, depending on fabrication techniques and processes that may permit such a small value for BW.

Referring now to FIG. 4, a cross-sectional view of an exemplary embodiment of a confinement well 220 of a display 200 is illustrated. The arrangement of FIG. 4 is similar to that described above with reference to FIG. 3A, with like numbers used to represent like elements except using the 200 series as opposed to the 100 series. As illustrated, however, the OLED display 200 also includes an additional surface feature 216 disposed in the gap S between electrodes 206, 208.

Surface feature 216 can be any structure that does not directly provide electrical current into the OLED films disposed over it, thereby comprising a non-active region of the pixel area between the active regions associated with the electrodes 206 and 208. For example, the surface feature 216 can further comprise an opaque material. As depicted in FIG. 4, a hole conducting layer 210 and organic light-emissive layer 212 can be deposited over a portion of such circuitry elements, as represented topographically by surface feature 216. In the case that surface feature 216 contains electrical elements, such elements may be further coated with an electrically insulating material so as to electrically isolate those elements from the OLED films deposited onto surface feature 216.

In an exemplary embodiment, surface feature 216 can include driving circuitry, including but not limited to, for